# MN3113F

Vertical Driver LSI for Video Camera CCD Area Image Sensor

## Overview

The MN3113F is a vertical driver LSI for a two-dimensional interline CCD image sensor. It features a built-in power supply circuit that, in conjunction with such external components as six booster capacitors and two voltage stabilization capacitors, produces stabilized +15.0V and -10.0V power supplies from a +5.0V input and HD pulses.

The MN3113F makes it possible to drive a CCD image sensor on a single 5 volt power supply.

#### Features

- Single 5 volt power supply

- Adjustable output voltage for regulated voltage circuit

- Applications

- Video cameras

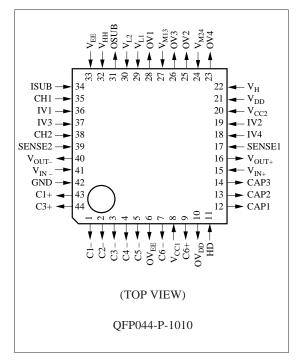

## Pin Assignment

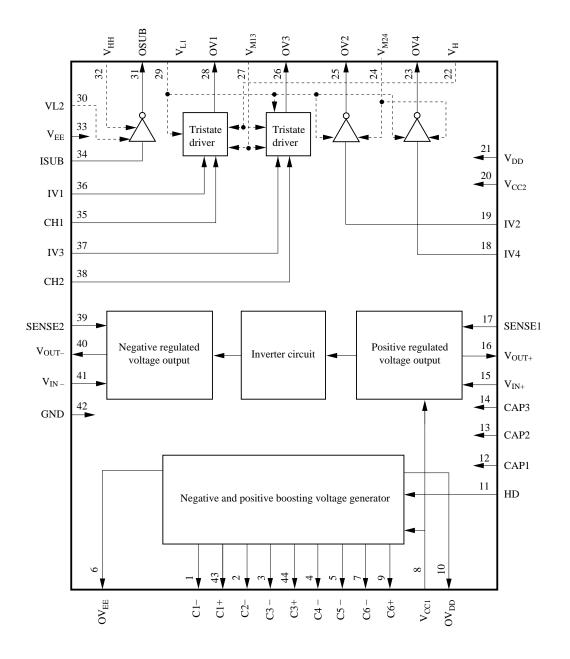

### Block Diagram

## Pin Descriptions

| Pin No. | Symbol            | Pin Name                   | I/O | Function Description                      |

|---------|-------------------|----------------------------|-----|-------------------------------------------|

| 8       | V <sub>CC1</sub>  | "H" level power supply     | Ι   | "H" level input for 5 volt circuits       |

| 20      | V <sub>CC2</sub>  | for input block            |     |                                           |

| 42      | GND               | "L" level power supply     | Ι   | "L" level input for 5 volt circuits       |

|         |                   | for input block            |     |                                           |

| 22      | V <sub>H</sub>    | "H" level power supply     | Ι   | "H" level input for high-voltage circuits |

|         |                   | for vertical driver        |     |                                           |

| 32      | V <sub>HH</sub>   | "H" level power supply     | Ι   | "H" level input for high-voltage circuits |

|         |                   | for SUB driver             |     |                                           |

| 27      | V <sub>M13</sub>  | "M" level power supply     | Ι   | "M" level input for high-voltage circuits |

| 24      | V <sub>M24</sub>  | for vertical driver        |     |                                           |

| 29      | V <sub>L1</sub>   | "L" level power supply     | Ι   | "L" level input for high-voltage circuits |

|         |                   | for vertical driver        |     |                                           |

| 30      | V <sub>L2</sub>   | "L" level input            | Ι   | "L" level input for high-voltage circuits |

|         |                   | for SUB driver             |     |                                           |

| 21      | V <sub>DD</sub>   | Power supply 1 for driver  | Ι   | "H" level for high-voltage circuits       |

| 33      | V <sub>EE</sub>   | Power supply 2 for driver  | Ι   | "L" level for high-voltage circuits       |

| 15      | V <sub>IN+</sub>  | Positive regulated voltage | Ι   | Positive regulated voltage block          |

|         |                   | block voltage input        |     | voltage input pin                         |

| 41      | V <sub>IN –</sub> | Negative regulated voltage | Ι   | Negative regulated voltage block          |

|         |                   | block voltage input        |     | voltage input pin                         |

| 11      | HD                | HD pulse input             | Ι   | HD pulse input pin                        |

| 19      | IV2               | Transfer pulse input       | Ι   | Charge transfer pulse input pin           |

| 18      | IV4               | Transfer pulse input       | Ι   | Charge transfer pulse input pin           |

| 36      | IV1               | Transfer pulse input       | Ι   | Charge transfer pulse input pin           |

| 37      | IV3               | Transfer pulse input       | Ι   | Charge transfer pulse input pin           |

| 35      | CH1               | Charge pulse input         | Ι   | Charge readout pulse input pin            |

| 38      | CH2               | Charge pulse input         | Ι   | Charge readout pulse input pin            |

| 34      | ISUB              | SUB pulse input            | Ι   | Unwanted charge rejection pulse input pin |

| 17      | SENSE1            | Positive voltage sensing   | Ι   | Positive voltage control sensing pin      |

|         |                   | input                      |     |                                           |

| 39      | SENSE2            | Negative voltage sensing   | Ι   | Negative voltage control sensing pin      |

|         |                   | input                      |     |                                           |

| 43      | C1+               | C1 connection              | 0   | Booster block voltage charging capacitor  |

| 1       | C1-               |                            |     | connection pins                           |

| 2       | C2+               | C2 connection              | 0   | Booster block voltage charging capacitor  |

|         | C2-               |                            |     | connection pins                           |

| 44      | C3+               | C3 connection              | 0   | Booster block voltage charging capacitor  |

| 3       | C3 –              |                            |     | connection pins                           |

| 4       | C4 –              | C4 connection              | 0   | Booster block voltage charging capacitor  |

|         |                   |                            |     | connection pins                           |

| 5       | C5 –              | C5 connection              | 0   | Booster block voltage charging capacitor  |

|         |                   |                            |     | connection pins                           |

## ■ Pin Descriptions (continued)

| Pin No. | Symbol            | Pin Name                                 | I/O Function Descrip |                                                                                                                                 |

|---------|-------------------|------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 7       | C6 –              | C6 connection pins                       | 0                    | Booster block voltage charging capacitor                                                                                        |

| 9       | C6+               |                                          |                      | connection pins                                                                                                                 |

| 10      | OV <sub>DD</sub>  | Booster block positive<br>voltage output | 0                    | Booster block positive voltage output pin                                                                                       |

| 6       | OV <sub>EE</sub>  | Booster block negative<br>voltage output | 0                    | Booster block negative voltage output pin                                                                                       |

| 16      | V <sub>OUT+</sub> | Positive regulated voltage output        | 0                    | Positive regulated voltage output pin                                                                                           |

| 40      | V <sub>OUT-</sub> | Negative regulated voltage output        | 0                    | Negative regulated voltage output pin                                                                                           |

| 23      | OV4               | Binary transfer pulse<br>output          | 0                    | $\begin{array}{c} Binary \left( V_{M24}  ,  V_{L1} \right) \text{ transfer pulse} \\ \text{output pin} \end{array}$             |

| 25      | OV2               | Binary transfer pulse<br>output          | 0                    | Binary $(V_{M24}, V_{L1})$ transfer pulse output pin                                                                            |

| 26      | OV3               | Tristate transfer pulse<br>output        | 0                    | $\begin{array}{c} Tristate \left( V_{H}  ,  V_{M13}  ,  V_{L1} \right) \text{ transfer pulse} \\ \text{output pin} \end{array}$ |

| 28      | OV1               | Tristate transfer pulse<br>output        | 0                    | $\begin{array}{c} Tristate (V_{H}, V_{M13}, V_{L1}) \text{ transfer pulse} \\ output pin \end{array}$                           |

| 31      | OSUB              | SUB pulse output                         | 0                    | Unwanted charge $(V_{HH}, V_{L2})$ rejection pulse input pin                                                                    |

| 12      | CAP1              | Stabilizing capacitor                    | 0                    | Pins for connecting capacitors for internal                                                                                     |

| 13      | CAP2              | connection                               |                      | voltage stabilization circuits                                                                                                  |

| 14      | CAP3              |                                          |                      |                                                                                                                                 |

## Functional Description

Binary transfer pulses (vertical driver block)

|     | ,   |

|-----|-----|

| IV2 | OV2 |

| IV4 | OV4 |

| Н   | L   |

| L   | М   |

|     |     |

## Tristate transfer pulses (vertical driver block)

| OV1 |

|-----|

| OV3 |

| L   |

| М   |

| L   |

| Н   |

|     |

\*1 IV1, IV2, IV3, IV4, CH1, CH2

OV1, OV2, OV3, OV4 H:  $V_H$ M:  $V_{M13}$ , or  $V_{M24}$ L:  $V_{L1}$

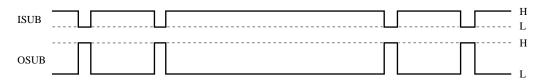

## Unwanted charge rejection pulses (SUB driver block)

| 0, 1               | (    |

|--------------------|------|

| ISUB               | OSUB |

| Н                  | L    |

| L                  | Н    |

| *1 ISUB            |      |

| H: V <sub>CC</sub> |      |

| L: GND             |      |

| OSUB               |      |

| H: V <sub>HH</sub> |      |

| L: V <sub>L2</sub> |      |

|                    |      |

H: V<sub>CC</sub> L: GND

#### Electrical Characteristics

#### (1) DC characteristics

$V_{\rm HH}\!\!=\!\!V_{\rm H}\!\!=\!\!15.0V$  ,  $V_{\rm M13}\!\!=\!\!V_{\rm M24}\!\!=\!\!1.0V$  , GND=0.0V ,

$V_{CC1}{=}V_{CC2}{=}5.0V$  (=V\_{CC}),  $V_{L1}$  =–7.0V ,  $V_{L2}$  =–10.0V , Ta=+25°C

|                                | , 112                                  | · · · · · · · · · · · · · · · · · · ·                          |                 |       |                  |      |  |

|--------------------------------|----------------------------------------|----------------------------------------------------------------|-----------------|-------|------------------|------|--|

| Parameter                      | Symbol                                 | Test conditions                                                | min             | typ   | max              | Unit |  |

| Quiescent supply current       | I <sub>DDST</sub>                      | V <sub>I</sub> =GND , V <sub>CC</sub>                          |                 | 2     | 4                | mA   |  |

| Operating supply current       | I <sub>DDDYN</sub>                     | V <sub>I</sub> =GND , V <sub>CC</sub>                          |                 | 45    | 90               | mA   |  |

| Power supply output pins       |                                        |                                                                |                 |       |                  |      |  |

| Positive voltage stabilization | V <sub>OUT+</sub>                      | V <sub>I</sub> =GND , V <sub>CC</sub> , I <sub>O</sub> =7mA    | 14.5            | 15.0  | 15.5             | V    |  |

| circuit output voltage         |                                        | f <sub>INHD</sub> =15.7kHz                                     |                 |       |                  |      |  |

| Negative voltage stabilization | V <sub>OUT-</sub>                      | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>O</sub> =-2mA    | -10.5           | -10.0 | -9.5             | V    |  |

| circuit output voltage         |                                        | f <sub>INHD</sub> =15.7kHz                                     |                 |       |                  |      |  |

| Input pins                     | IV1                                    | , IV2 , IV3 , IV4 , CH1 , CH2 , ISU                            | B, HD           |       |                  |      |  |

| "H" level voltage              | V <sub>IH</sub>                        |                                                                | 3.5             |       | V <sub>CC</sub>  | V    |  |

| "L" level voltage              | V <sub>IL</sub>                        |                                                                | GND             |       | 1.5              | V    |  |

| Input leak current             | I <sub>LI</sub>                        | V <sub>I</sub> =0 to 5V                                        |                 |       | ±1               | μΑ   |  |

| Output pins 1 (Binary output   | Output pins 1 (Binary output) OV2, OV4 |                                                                |                 |       |                  |      |  |

| Output voltage "M" level       | V <sub>OM1</sub>                       | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>OM1</sub> =-1mA  | 0.9             |       | V <sub>M24</sub> | V    |  |

| Output voltage "L" level       | V <sub>OL1</sub>                       | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>OL1</sub> =1mA   | V <sub>L1</sub> |       | -6.9             | V    |  |

| Output on resistance "M" level | R <sub>ONM1</sub>                      | I <sub>OM1</sub> =-50mA                                        |                 |       | 40               | Ω    |  |

| Output on resistance "L" level | R <sub>ONL1</sub>                      | I <sub>OL1</sub> =50mA                                         |                 |       | 40               | Ω    |  |

| Output pins 2 (Tristate output | it) OV                                 | 1 , OV3                                                        |                 |       |                  |      |  |

| Output voltage "H" level       | V <sub>OH2</sub>                       | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>OH2</sub> =-1mA  | 14.9            |       | V <sub>H</sub>   | V    |  |

| Output voltage "M" level       | V <sub>OM2</sub>                       | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>OM2</sub> =-1mA  | 0.9             |       | V <sub>M13</sub> | V    |  |

| Output voltage "L" level       | V <sub>OL2</sub>                       | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>OL2</sub> =1mA   | V <sub>L1</sub> |       | -6.9             | V    |  |

| Output on resistance "H" level | R <sub>ONH2</sub>                      | I <sub>OH2</sub> =-50mA                                        |                 |       | 50               | Ω    |  |

| Output on resistance "M" level | R <sub>ONM2</sub>                      | I <sub>OM2</sub> =±50mA                                        |                 |       | 40               | Ω    |  |

| Output on resistance "L" level | R <sub>ONL2</sub>                      | I <sub>OL2</sub> =50mA                                         |                 |       | 40               | Ω    |  |

| Output pin 3 (SUB output)      | OSU                                    | JB                                                             |                 |       |                  |      |  |

| Output voltage "H" level       | V <sub>OHH3</sub>                      | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>OHH3</sub> =-1mA | 14.9            |       | V <sub>HH</sub>  | V    |  |

| Output voltage "L" level       | V <sub>OL3</sub>                       | V <sub>I</sub> =GND, V <sub>CC</sub> , I <sub>OL3</sub> =1mA   | V <sub>L2</sub> |       | -9.9             | V    |  |

| Output on resistance "H" level | R <sub>ONHH3</sub>                     | I <sub>ONHH3</sub> =-50mA                                      |                 |       | 50               | Ω    |  |

| Output on resistance "L" level | R <sub>ONL3</sub>                      | I <sub>ONL3</sub> =50mA                                        |                 |       | 40               | Ω    |  |

## (2) AC characteristics

$V_{\rm HH}\!\!=\!\!V_{\rm H}\!\!=\!\!15.0V$  ,  $V_{\rm M13}\!\!=\!\!V_{\rm M24}\!\!=\!\!1.0V$  , GND=0.0V ,

$V_{CC1}{=}V_{CC2}{=}5.0V\;({=}V_{CC})$  ,  $V_{L1}{=}{-}7.0V$  ,  $V_{L2}{=}{-}10.0V$  , Ta=+25°C

| Parameter                    | Symbol            | Test Conditions             | min | typ | max | Unit |

|------------------------------|-------------------|-----------------------------|-----|-----|-----|------|

| Output pins 1 (Binary outpu  | t) OV             | 2 , OV4                     |     |     |     |      |

| Transmission delay time      | t <sub>PLM</sub>  | No load                     |     | 100 | 200 | ns   |

|                              | t <sub>PML</sub>  | From "L" level to "M" level |     |     |     |      |

| Rise time                    | t <sub>TLM</sub>  |                             |     | 200 | 300 | ns   |

| Fall time                    | t <sub>TML</sub>  |                             |     |     |     |      |

| Output pins 2 (Tristate outp | ut) OV            | 1 , OV3                     |     | *   | *   |      |

| Transmission delay time      | t <sub>PLM</sub>  | No load                     |     | 100 | 200 | ns   |

|                              | t <sub>PML</sub>  | From "L" level to "M" level |     |     |     |      |

| Transmission delay time      | t <sub>PMH</sub>  | No load                     |     | 200 | 400 | ns   |

|                              | t <sub>PHM</sub>  | From "M" level to "H" level |     |     |     |      |

| Rise time                    | t <sub>TLM</sub>  |                             |     | 200 | 300 | ns   |

| Fall time                    | t <sub>TML</sub>  |                             |     |     |     |      |

| Rise time                    | t <sub>TMH</sub>  |                             |     | 200 | 300 | ns   |

| Fall time                    | t <sub>THM</sub>  |                             |     |     |     |      |

| Output pin 3 (SUB output)    | OSU               | JB                          |     |     |     |      |

| Transmission delay time      | t <sub>PLHH</sub> | No load                     |     | 100 | 200 | ns   |

|                              | t <sub>PHHL</sub> | From "L" level to "H" level |     |     |     |      |

| Risie time                   | t <sub>TLHH</sub> |                             |     | 200 | 300 | ns   |

| Fall time                    | t <sub>THHL</sub> |                             |     |     |     |      |

----- Н

---- L

L M

Η

L M

- L

- H

L

Н

L

Μ

Η

L H

-- L

- H - M

- L

-- L

--- Н

\_ \_ \_ \_ \_ \_ \_ \_ \_

\_ \_ \_ \_ \_ \_ \_ \_ \_

## Timing Chart

- 1. Binary transfer pulses 63.5µs 254µs 63.5µs 2µs IV2 OV2 2. Binary transfer pulses IV4 OV4 3. Tristate transfer pulses IV1 3µs |-CH1 OV1 4. Tristate transfer pulses IV3 CH2 OV3

- 5. SUB pulses

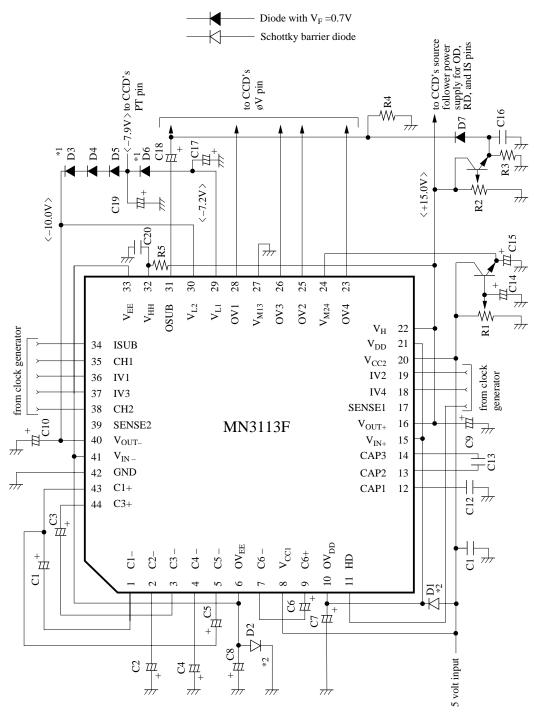

#### Application Circuit Example

Notes

\*1: These diodes must have a  $V_F$  of 0.7V.

\*2: These diodes must be Schottky barrier diodes (MA723).

<sup>\*3:</sup> The booster circuit's electrolytic capacitors (C1 to C8) and voltage stabilization capacitors (C9 and C10) must have little impedance fluctuation at low temperatures.

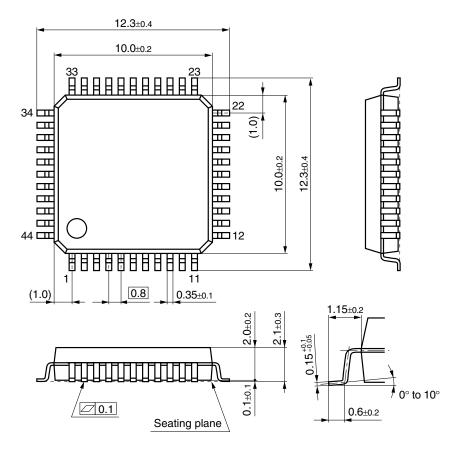

## Package Dimensions (Unit: mm)

#### QFP044-P-1010

Note) The package of this product will be changed to lead-free type (QFP044-P-1010E). See the new package dimensions section later of this datasheet.

## Usage Notes

#### External components

This product requires two Schottky barrier diodes. We recommend the following components.

Schottky barrier diodes: MA723 or equivalents

Ta=25°C

| Component               | Model number | Typical characteristics                      | Notes |

|-------------------------|--------------|----------------------------------------------|-------|

| Schottky barrier diodes | MA723        | $I_F = 200 \text{mA}, V_F \le 0.55 \text{V}$ |       |

The MN3113F will not operate properly if the components do not satisfy the above specifications.

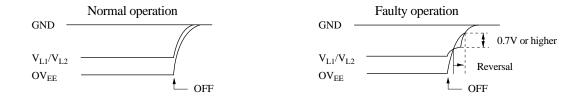

2. Always use the specified components for peripheral circuits so as to ensure that  $OV_{EE}$  and  $V_L$  do not reverse potentials when the power is turned off.

As the above sketch illustrates, allowing  $OV_{EE}$  to exceed  $V_{L1}$  and  $V_{L2}$  by more than 0.7 V produces the risk of applying a forward bias to the PN junction, turning on the parasitic transistor, and generating an overcurrent that produces latch-up.

If this phenomenon arises, increase the size of capacitor C8 or decrease the size of capacitor C10 to increase the  $OV_{EE}$  time constant.

(See the sample application circuit for the locations of C8 and C10.)

3. Adjusting boost voltages with SENSE pins

The MN3113F provides the SENSE pins, SENSE1 and SENSE2, for adjusting the boost voltages ( $V_{OUT+}$  and  $V_{OUT-}$ ) with the following procedures.

Adjusting the positive boosted voltage

(1) Making  $V_{OUT+} < 15V$

Insert a resistor, R, between the SENSE1 pin (pin 17) and the  $V_{OUT+}$  pin (pin 16). The theoretical output voltage at the  $V_{OUT+}$  pin is then given by the following formula.

$$V_{OUT+'} = V_{CC} x \frac{50k\Omega + 100k\Omega//R}{50k\Omega}$$

(where 100 k $\Omega$ //R is the effective resistance of the 100 k $\Omega$  resistor and R connected in parallel.)

For example, if R is 50 k $\Omega$ ,

$$V_{OUT+'} = 5 \times \frac{50k\Omega + 33.3k\Omega}{50k\Omega} = 8.3V$$

(2) Making  $V_{OUT+} > 15V$

Insert a resistor, R, between the SENSE1 pin (pin 17) and the GND pin (pin 42).

$$V_{OUT+'} = V_{CC} \times \frac{50k\Omega//R + 100k\Omega}{50k\Omega//R}$$

Adjusting the negative boosted voltage

(1) Making  $V_{OUT-} < -10V$

Insert a resistor, R, between the SENSE2 pin (pin 39) and the GND pin (pin 42).

$$V_{OUT-'} = V_{CC} \times \frac{50k\Omega//R + 50k\Omega}{50k\Omega//R}$$

(2) Making  $V_{OUT-} > -10V$

Insert a resistor, R, between the SENSE2 pin (pin 39) and the V<sub>OUT-</sub> pin (pin 40).

$$V_{OUT-'} = -V_{CC} \times \frac{50k\Omega + 50k\Omega//R}{50k\Omega}$$

For example, if R is 50 k $\Omega$ ,

$$V_{OUT-'} = -5 \times \frac{50k\Omega + 25k\Omega}{50k\Omega} = -7.5V$$

Note, however, that the above formulas are mere guidelines, that the internal resistances vary between samples, and that therefore each sample will have to be adjusted.

Note also that booster circuit capacity and output load current impose limits on adjustments for boosting  $V_{OUT+}$  above 15V and  $V_{OUT-}$  below –10V.

(The maximum possible adjustments are 20V for  $V_{OUT+}$  and –15V for  $V_{OUT-}.)$

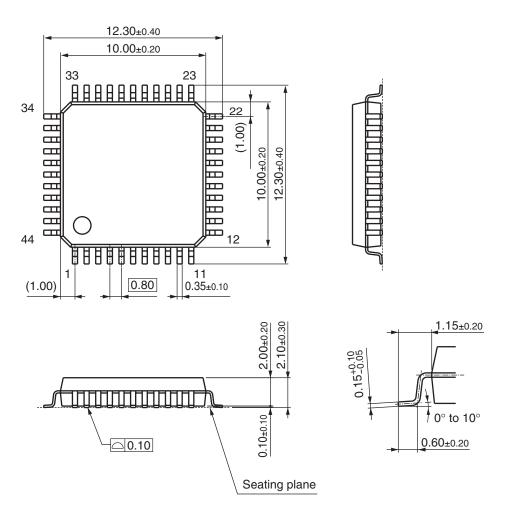

- New Package Dimensions (Unit: mm)

- QFP044-P-1010E (Lead-free package)

## Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

## Please read the following notes before using the datasheets

- A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use. Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.