# **OKI** semiconductor

# MSM5840

### **CMOS 4-BIT SINGLE CHIP MICROCONTROLLER**

### **GENERAL DESCRIPTION**

The OKI MSM5840 microcontroller is a low-power, high-performance single chip device implemented in complementary metal oxide semiconductor technology. Integrated within this one chip are 16K bits of mask program ROM, 512 bits of data RAM, 30 Input/Output lines, a programmable timer/counter, and oscillator. Program memory is byte wide and data-paths are organized in 4 bit nibbles. RAM and I/O lines are bit addressable. Up to 4K of external ROM interfaces to the 8 bit bidirectional bus. 98 instructions include binary, BCD, logical operations; bit set, reset, test, 8 bit I/O; relative jumps; multifunctional instructions (increment, modify, skip); 8 bit wide table output; subroutine call and return. 94% of instructions are single byte, single cycle operations.

### **FEATURES**

- Low Power Consumption − 8mW Typical

- 100% Static Logic 50μW Standby, Typical

- 2K × 8 Internal ROM

- Up to 4K × 8 External ROM

- 128 × 4 Internal RAM

- 30 I/O Lines Incl. 8 Bit Data Bus

- Programmable 8 Bit Timer/Counter

- Self-contained Oscillator

- 98 Instructions

- Expandable Memory and I/O

- 2 Interrupt Levels

- 4 Stack Levels

- Operating Temperature -40° to +85°C

- 3V to 6V Operating VDD

- Battery Powered or Battery Backup

- TTL Compatible (with pullups)

- 7.6μs Cycle Time @4.2MHz (Vpp 5V± 10%)

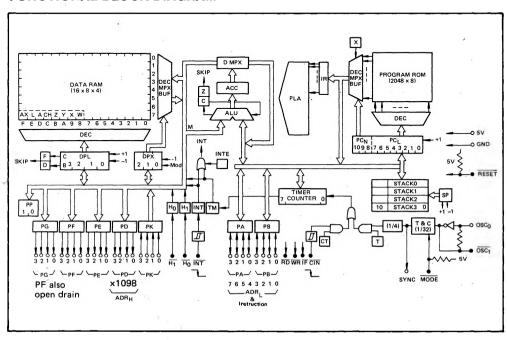

## **FUNCTIONAL BLOCK DIAGRAM**

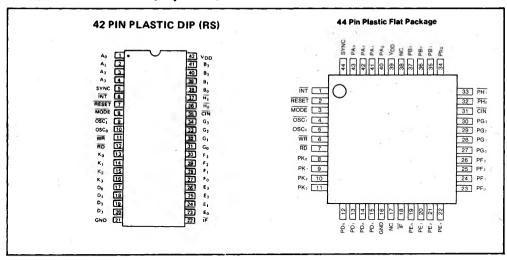

# PIN CONFIGURATION (Top View)

# **PIN DESCRIPTION**

| Designation       | Pin No.              | Function                                                                                                                                                                                                                 |

|-------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND               | 21                   | Circuit GND potential                                                                                                                                                                                                    |

| V <sub>DD</sub>   | 42                   | Main power source (+5V)                                                                                                                                                                                                  |

| OSC <sub>0</sub>  | 10                   | Crystal OSC input, external clock input                                                                                                                                                                                  |

| OSC <sub>1</sub>  | 9                    | Crystal OSC input, external clock output (not TTL compatible)                                                                                                                                                            |

| PA, PB            | 1 to 4<br>38 to 41   | Pseudo-bidirectional ports for 4-bit parallel I/O. Used as a pair for 8-bit I/O. Used to output 8 LSBs of address in external ROM mode. Used to read external instruction during IF.                                     |

| PD, PE,<br>PE, PG | 17 to 20<br>23 to 34 | Output ports for 4-bit parallel output and bit set/reset. Specified by internal port pointer, Bit position specified by set/reset instruction. PD also used for instruction address MSBs in external ROM mode during IF. |

| PK                | 13 to 16             | 4-bit parallel or bit test input port (unlatched)                                                                                                                                                                        |

| PH                | 36 and 37            | 2-bit input port with latched memory (negative level sensitive)                                                                                                                                                          |

| RESET             | 7                    | RESET has priority over every other signal. (see MSM5840 user's manual for initialization sequence)                                                                                                                      |

| MODE              | 8                    | Used to enable external ROM mode during RESET and also to enable STOP mode during execution (for stepping program)                                                                                                       |

| ĪNT               | 6                    | Negative edge sensitive external interrupt signal associated with El and Dl instructions. Vectors to location 200H.                                                                                                      |

| CIN               | 35                   | Negative edge sensitive external input for counter associated with ECT and DCT instructions. Vectors to location 100H. (same as timer)                                                                                   |

| SYNC              | 5                    | General purpose synchronizing signal output at the beginning of each machine cycle. Used for address strobe during external ROM mode.                                                                                    |

| RD                | 12                   | Read strobe pulse occuring when port A or B is read (1A, 1B, 1AB)                                                                                                                                                        |

| WR                | 11 -                 | Write strobe pulse occurring when port A or B is written (OA, OB, OAB, OBS, OTD)                                                                                                                                         |

| ĪF                | 22                   | Read strobe pulse occurring during an instruction fetch from external ROM.                                                                                                                                               |

#### **FUNCTIONAL DESCRIPTION**

**Program ROM**

The MSM5840 will address up to 4K bytes of program ROM and can have 2K bytes of internal masked ROM, or all ROM may be located externally. External EPROM may be used for program development with conversion to internal ROM occurring after program debug and system checkout and verification. All instructions are byte wide. Only three of the 98 instructions require two bytes of program code. The instructions are routed to a programmed logic array which generates the necessary internal control signals.

#### **Data RAM**

Data is organized in 4 bit nibbles. Internal data RAM consists of 128 nibbles, 8 nibbles of which are dedicated registers accessible directly under program control. These are the general purpose registers, W, X, Y and Z, and the 4 save (exchange) registers, CH, A, L, and AX. All other DATA RAM must be addressed indirectly through the DP (data pointer) registers, a seven bit pointer (directly accessible by numerous instructions) consisting of 4 bit DPL register and a 3 bit DPH register. Any nibble of internal data RAM can be accessed through the DP registers. Some instructions automatically change the contents of the DP registers allowing efficient array processing.

Input/Output Ports

PA, PB — These two ports are pseudobidirectional ports which can be used as simple I/O lines or used as either a 4-bit or 8-bit parallel bus. An instruction fetches the external ROM data through these ports by outputting the 8 low order bits of address during SYNC followed by an IF (instruction fetch) cycle. In addition, synchronized data transfers are possible through these ports with the I/O pin signals RD and WR associated with certain input/output instructions dedicated to these ports. In short, PA and PB can be used as a multiplexed address/instruction/data bus.

PD, PE, PF, PG — These four output ports are addressed indirectly through the TWO BIT port pointer whose contents are changed through certain instructions. These ports are bit (set/reset) addressable. PD is also used for the high order bits of address during an external instruction fetch. PF and PG are open drain outputs and PG is set high by a hardware RESET.

PK is an input port without memory, addressable either as a nibble or bit level input.

PH is a two-bit input port with memory, which can be tested and reset under program control.

**External Interrupt**

The INT pin can be tested under program control or enabled to cause a vectored interrupt to location 200H. It is negative edge sensitive.

#### Timer/Counter

The timer/counter is an 8-bit counter whose input is selected under program control to be either an external signal (CIN) or an internal square wave of 1/128 the frequency of the OSCo input (2 MHz/128 = 15.625 kHz). The timer/counter can be enabled or disabled under program control as can be associated internal interrupt which vectors to location 100H and has higher priority than the external interrupt.

#### Stack

The stack is an LIFO queue for storing returnfrom-interrupt and return-from-subroutine address information. It is eleven bits wide and 4 levels deep.

**Program Counter (PC)**

The program counter is 11 bits wide and loaded under program control.

#### **Accumulator**

The accumulator register is the data path focal point of the CPU. Approximately one-half of the instructions involve the accumulator. Its contents are the source and destination for many ALU operations and port operations. CASE statements (computed GOTOs) are possible by using the Jump with Accumulator (JA) instruction.

Flags

The MSM5840 is endowed with the following set of flags.

Z - zero flag

Indicates that the result of the previous operation was zero

F - all ones

Indicates a carry from the DP<sub>1</sub> register

O – all zeros : Indicates a borrow from the DP<sub>I</sub> register

C – carry : Indicates a carry from the previous operation

T - timer : Indicates that the timer/ counter is specified as a timer

CT - counter : Indicates that the timer/ counter is specified as a counter

TM – timer flag : Indicates an overflow of the timer/counter register

INT – interrupt : Latching memory flag for the external interrupt INTE – interrupt : Indicates that interrupts

enable have been enabled

Ho - Ho memory Indicates that an input

has been detected on the

Ho input

Ho same as Ho except Ho

input

X : 0 indicates internal ROM

: 0 indicates internal ROM, 1 indicates external ROM. If all external ROM, 0 indicates first bank of 2K.

# **INSTRUCTION SET**

| Mnemonic                       |     | Description                                                                           |         | 1       | nstr    | ucti    | on (    | Code                | е        |         | Byte | Cycle |

|--------------------------------|-----|---------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------------------|----------|---------|------|-------|

|                                |     | Description                                                                           | 7       | 6.      | 5       | 4       | 3       | 2                   | 1        | 0       | Бую  | Cyc   |

| Ì                              | CLA | Clear Accumulator                                                                     | 0       | .0      | 0       | 1       | 0       | 0                   | 0        | 0       | 1    | 1     |

| ١                              | CLL | Clear DP <sub>L</sub>                                                                 | 0       | 0       | 1       | 0       | 0       | 0                   | 0        | 0       | 1    | 1     |

|                                | CLH | Clear DP <sub>H</sub>                                                                 | 0       | 1       | 1       | 0       | 0       | 0                   | 0        | 0       | 1    | 1     |

|                                | LAI | Load Accumulator with Immediate                                                       | 0       | 0       | 0       | 1       | la      | 12                  | h        | lo      | 1 1  | 1     |

|                                | LLI | Load DP <sub>L</sub> with Immediate                                                   | 0       | 0       | 1       | 0       | lз      | 12                  | lэ       | lo      | 1    | 1     |

| 1                              | LHI | Load DP <sub>H</sub> with Immediate                                                   | 0       | 1       | 1       | 0       | Ó       | 12                  | Тı       | lo      | 1    | 1     |

| 1                              | L   | Load Accumulator with Memory                                                          | 1       | 0       | 0       | 1       | 0       | 1                   | 0        | 0       | 1    | 1     |

| 1                              | LM  | Load Accumulator with Memory then Modify DPH                                          | 1       | 0       | 0       | 1       | 0       | 1                   | h        | lo      | 1    | 1     |

|                                | LAL | Load Accumulator with DPL                                                             | 0       | 1       | 0       | 1       | 0       | 1                   | 0        | 1       | 1    | 1     |

|                                | LLA | Load DPL with Accumulator                                                             | 0       | 1       | 0       | 1       | 0       | 1                   | 0        | 0       | 1    | 1     |

|                                | LAW | Load Accumulator with W Register                                                      | 1       | 0       | 0       | 0       | 0       | 1                   | 0        | 0       | 1    | 1     |

| î                              | LAX | Load Accumulator with X Register                                                      | 1       | 0       | 0       | 0       | 0       | 1                   | 0        | 1       | 1    | 1     |

| and charles and charles        | LAY | Load Accumulator with Y Register                                                      | 1       | 0       | 0       | 0       | 0       | 1                   | 1        | 0       | 1    | 1     |

|                                | LAZ | Load Accumulator with Z Register                                                      | 1       | 0       | 0       | 0       | 0       | 1                   | 1        | 1       | 1    | 1     |

|                                | SI  | Store Accumulator to Memory then Increment DPL                                        | 1       | 0       | 0       | 1       | 0       | 0                   | 0        | 0       | 1    | 1     |

|                                | SMI | Store Accumulator to Memory then Modify DP <sub>H</sub> and Increment DP <sub>L</sub> | 1       | 0       | 0       | 1       | 0       | 0                   | h        | lo      | 1    | 1     |

| 1                              | LWA | Load W Register with Accumulator                                                      | 1       | 0       | 0       | 0       | 0       | 0                   | 0        | 0       | 1    | 1     |

| 1                              | LXA | Load X Register with Accumulator                                                      | 1       | 0       | 0       | 0       | 0       | 0                   | 0        | 1       | 1    | 1     |

|                                | LYA | Load Y Register with Accumulator                                                      | 1       | 0       | 0       | 0       | 0       | 0                   | 1        | 0       | 1    | 1     |

| 1                              | LZA | Load Z Register with Accumulator                                                      | 1       | 0       | 0       | 0       | 0       | 0                   | 1        | 1       | 1    | 1     |

| Ì                              | LPA | Load Port Pointer with Accumulator                                                    | О       | 1       | 0       | 1       | 1       | 0                   | 0        | 0       | 1    | 1     |

|                                | LTI | Load Timer with Immediate                                                             | 0<br>I7 | 1<br>16 | 1<br>15 | 0<br>I₄ | 1<br>Ia | 0<br>1 <sub>2</sub> | 0<br>  1 | 0<br>lo | 2    | 1     |

| 1                              | RTH | Read Timer H                                                                          | 0       | 1       | 1       | 0       | 1       | 0                   | 1        | 0       | 1    | 1     |

| 1                              | RTL | Read timer L                                                                          | 0       | 1       | 1       | 0       | 1       | 0                   | 1        | 1       | 1    | 1     |

| 1                              | XA  | Exchange Accumulator with Save Register A                                             | 0       | 1       | 0       | 0       | 1       | 0                   | 0        | 1       | 1    |       |

|                                | XL  | Exchange DP <sub>1</sub> with Save Register L                                         | 0       | 1       | 0       | 0       | 1       | 0                   | 1        | 0       | 1    | ١ ،   |

| 3                              | хсн | Exchange DP <sub>H</sub> and Carry with Save Register CH                              | 0       | 1       | 0       | 0       | 1       | 0                   | 0        | 0       | 1    | 1     |

| B                              | X   | Exchange Accumulator with Memory                                                      | 1       | 0       | 0       | 1       | 1       | 0                   | 0        | 0       | 1    |       |

| ֓֞֜֜֜֞֜֜֜֜֞֜֜֜֜֜֡֓֓֜֜֜֡֓֓֓֜֜֡֡ | хм  | Exchange Accumulator with Memory then Modify DPH                                      | 1       | 0       | 0       | 1       | 1       | 0                   | Ιı       | lo      | 1    |       |

|                                | XAX | Exchange Accumulator with Save Register AX                                            | 0       | 1       | 0       | 0       | 1       | 0                   | 1        | 1       | 1    |       |

| ,                              | INA | Increment Accumulator                                                                 | 0       | 0       | 0       | 0       | 0       | 0                   | 0        | 1       | 1    | Τ.    |

|                                | INL | Increment DPL                                                                         | 0       | 1       | 0       | 1       | 0       | 1                   | 1        | 1       | 1    | ١.    |

| 5                              | INM | Increment Memory                                                                      | 0       | 1       | 0       | 1       | 1       | 1                   | 0        | 1       | 1    |       |

|                                | INW | Increment W Register Skip if Zero                                                     | 1       | 0       | 0       | 0       | 1       | 0                   | 0        | 0       | 1    |       |

| 5                              | INX | Increment X Register                                                                  | 1       | 0       | 0       | 0       | 1       | 0                   | 0        | 1       | 1    | j .   |

| iliciali ped dilaman           | INY | Increment Y Register                                                                  | 1       | 0       | 0       | 0       | 1       | 0                   | 1        | 0       | 1    |       |

| ≝ [                            | INZ | Increment Z Register                                                                  | 1       | 0       | 0       | 0       | 1       | 0                   | 1        | 1       | 1    |       |

# **INSTRUCTION SET (CONT.)**

| ٨                  | Anemonic | Description                                               |     | 1 | nstr | ucti | on ( | Code |     |    | Byte | Cycle |

|--------------------|----------|-----------------------------------------------------------|-----|---|------|------|------|------|-----|----|------|-------|

|                    |          |                                                           | 7   | 6 | 5    | 4    | 3    | 2    | 1   | 0  | Dyte | 0,010 |

|                    | DCA      | Decrement Accumulator – Skip if Not All Ones              | 0   | 0 | 0    | 0    | 1    | 1    | 1   | 1  | 1    | 1     |

| ent                | DCL      | Decrement DPL                                             | 0   | 1 | 0    | 1    | 0    | 1    | 1   | 0  | 1    | 1     |

| ren                | DCM      | Decrement Memory                                          | 0   | 1 | 0    | 1    | 1    | 1    | 0   | 0  | 1    | 1     |

| ğ                  | DCW      | Decrement W Register Skip if All Ones                     | 1   | 0 | 0    | 0    | 1    | 1    | 0   | 0  | 1    | 1     |

| ent/               | DCX      | Decrement X Register                                      | 1   | 0 | 0    | 0    | 1    | 1    | 0   | 1  | 1    | 1     |

| ncrement/Decrement | DCY      | Decrement Y Register                                      | 1   | 0 | 0    | 0    | 1    | 1    | 1   | 0  | 1    | 1     |

| lic                | DCZ      | Decrement Z Register J                                    | 1   | 0 | 0    | 0    | 1    | 1    | 1   | 1  | 1    | 1     |

|                    | DCH      | Decrement DP <sub>H</sub> – Skip if All Ones and C = Zero | 0   | 1 | 0    | 1    | 1    | 1    | 1   | 1  | 1    | 1     |

|                    | CAO      | Complement Accumulator of One                             | 0   | 1 | 0    | 1    | 0    | 0    | 0   | 0  | 1    | 1     |

| ā                  | AND      | And Accumulator with Memory                               | 0   | 1 | 0    | 0    | 0    | 1    | 0   | 0  | 1    | 1     |

| ogical             | OR       | Or Accumulator with Memory                                | 0   | 1 | 0    | 0    | 0    | 1    | 0   | 1  | 1    | 1     |

| 7                  | EOR      | Exclusive or Accumulator with Memory                      | 0   | 1 | 0    | 0    | 0    | 1    | 1   | 0  | 1    | 1     |

|                    | RAL      | Rotate Accumulator Left through Carry                     | o   | 1 | 0    | 0    | 0    | 1    | 1   | 1  | 1    | 1     |

|                    | AC       | Add Memory to Accumulator with Carry                      | 0   | 1 | 0    | 0    | 1    | 1    | 0   | 0  | 1    | 1     |

|                    | ACS      | Add Memory to Accumulator with Carry, Skip if Carry       | 0   | 1 | 0    | 0    | 1    | 1    | 0   | 1  | 1    | 1     |

|                    | AS       | Add Memory to Accumulator, Skip if Carry                  | 0   | 1 | 0    | 0    | 1    | 1    | 1   | 0  | 1    | 1     |

| ţic                | AIS      | Add Immediate to Accumulator, Skip if Carry               | 0   | 0 | 0    | 0    | lз   | 12   | Тı  | lo | 1    | 1     |

| Arithmetic         | DAS      | Decimal adjust Accumulator in Subtraction                 | 0   | 1 | 0    | 1    | 1    | 0    | 1   | 0  | 1    | 1     |

| Arit               | СМ       | Compare Accumulator with Memory, Skip if Equal            | 0   | 1 | 0    | 1    | 1    | 1    | 1   | 0  | 1    | - 1   |

|                    | AWS      | Add W Register to Accumulator, Skip if Carry              | 1   | 0 | 0    | 1    | 1    | 1    | 0   | 0  | 1    | 1     |

|                    | AXS      | Add X Register to Accumulator, Skip if Carry              | 1   | 0 | 0    | 1    | 1    | 1    | 0   | 1  | 1    | 1     |

|                    | AYS      | And Y Register to Accumulator, Skip if Carry              | 1   | 0 | 0    | 1    | 1    | 1    | 1   | 0  | 1    | 1     |

|                    | AZS      | Add Z Register to Accumulator, Skip if Carry              | 1   | 0 | 0    | 1    | 1    | 1    | 1   | 1  | 1    | 1     |

|                    | SPB      | Set Port Bit                                              | 1   | 0 | 1    | 1    | 0    | 0    | 11  | lo | 1    | 1     |

|                    | RPB      | Reset Port Bit                                            | 1   | 0 | 1    | 1    | 0    | 1    | Ιı  | lo | 1    | 1     |

|                    | SMB .    | Set Memory Bit                                            | 1   | 0 | 1    | 1    | 1    | 0    | Ιı  | lo | 1    | 1     |

|                    | RMB      | Reset Memory Bit                                          | 1   | 0 | 1    | 1    | 1    | 1    | 11  | lo | 1    | 1     |

| est                | TAB      | Test Accumulator Bit                                      | 1   | 0 | 1    | 0    | 0    | 0    | ١'n | lo | 1    | 1     |

| Set/Reset/Tes      | тмв      | Test Memory Bit                                           | 1   | 0 | 1    | 0    | 0    | 1    | Ьı  | lo | 1    | 1     |

| Res                | ткв      | Test K Port Bit                                           | 1   | 0 | 1    | 0    | 1    | 0    | Ιı  | lo | 1    | 1     |

| Set/               | тнв      | Test H Port Bit > Skip if One                             | 1   | 0 | 1    | 0    | 1    | 1    | 0   | lo | 1    | 1     |

| BitS               | TI       | Test Interrupt flag                                       | - 1 | 0 | 1    | 0    | 1    | 1    | 1   | 1  | 1    | 1     |

| _                  | TTM      | Test Time flag                                            | 1   | 0 | 1    | 0    | 1    | 1    | 1   | 0  | 1    | 1     |

|                    | тс       | Test Carry flag                                           | О   | 1 | 0    | 0    | 0    | 0    | 1   | 0  | 1    | 1     |

|                    | sc       | Set Carry flag                                            | О   | 1 | 0    | 0    | 0    | 0    | 0   | 0  | 1    | 1     |

|                    | RC       | Reset Carry flag                                          | 0   | 1 | 0    | 0    | 0    | 0    | 0   | 1  | 1    | 1     |

# INSTRUCTION SET (CONT.)

|                   | Anemonic  | Description                                             |         | 1       | nstr    | ucti    | on (    | Code        | =         |         | Byte | 0     |

|-------------------|-----------|---------------------------------------------------------|---------|---------|---------|---------|---------|-------------|-----------|---------|------|-------|

|                   | vinemonic | Description                                             | 7       | 6       | 5       | 4       | 3       | 2           | 1         | 0       | Вуте | Cycle |

| ıtine             | J         | Jump                                                    | 0<br>I7 | 0<br>Is | 1<br> s | 1<br> 4 | 0<br>I3 | l 10<br>l 2 | ls<br>Iı  | e<br>Io | 2    | 2     |

| prou              | JC        | Jump in Current Page                                    | 1       | 1       | ls      | 14.     | . la    | 12          | Īı        | lo      | 1    | 1     |

| /Sul              | JA        | Jump with Accumulator                                   | 0       | 1       | 0       | 0       | 0       | 0           | 1         | 1       | 1    | 1     |

| Branch/Subroutine | CAL       | Call Subroutine                                         | 0<br>17 | 0<br>16 | 1<br> s | 1<br> 4 | 1<br>13 | l 10<br>l 2 | l9<br>  1 | e<br>Io | 2    | 2     |

| Ш                 | RT        | Return from Subroutine                                  | 0       | 1       | 0       | 1       | 1       | 0           | 0         | 1       | 1    | 2 -   |

|                   | OBS       | Output Byte String                                      | 0       | 1       | 1       | 1       | 0       | 0           | 0         | 0       | 1    | 2~17  |

|                   | OTD       | Output Table Data                                       | 0       | 1       | 1       | 1       | 0       | 0           | 0         | 1       | 1    | 2     |

|                   | OA        | Output Accumulator to Port A                            | 0       | 1       | 1       | 1       | 0       | 0           | 1         | 0       | 1    | 1     |

| +                 | ОВ        | Output Accumulator to Port B                            | 0       | 1       | 1       | 1       | 0       | 0           | 1         | 1       | 1    | 1     |

| nput/Output       | OP        | Output Accumulator to Port P designated Port<br>Pointer | 0       | 1       | 1       | 1       | 0       | 1           | 0         | 0       | 1    | 1     |

| put               | OAB       | Output Memory and Accumulator to Ports A and B          | 0       | 1       | 1       | 1       | 0       | 1           | 0         | 1       | 1    | 1     |

| =                 | ОРМ       | Output Memory to Port P designated Port Pointer         | 0       | 1       | 1       | 1       | 0       | 1           | 1         | 0       | 1    | 1     |

|                   | IA        | Input Port A in Accumulator                             | 0       | 1       | 1       | 1       | 1       | 0           | 1         | 0       | 1    | 1     |

|                   | ΙB        | Input Port B in Accumulator                             | 0       | 1       | 1       | 1       | 1       | 0           | 1         | 1       | 1    | 1     |

|                   | IK        | Input Port K in Accumulator                             | 0       | 1       | 1       | 1       | 1       | 1           | 0         | 0       | 1    | 1     |

|                   | IAB       | Input Ports A and B in Memory and Accumulator           | 0       | 1       | 1       | 1       | 1       | 1           | 0         | 1       | 1    | 1     |

|                   | EI        | Enable Interrupt                                        | 0       | 1       | 0       | 1       | 0       | 0           | 1         | 1       | 1    | 1     |

|                   | DI        | Disable Interrupt                                       | 0       | 1       | 0       | 1       | 0       | 0           | 1         | 0       | 1    | 1     |

|                   | ET        | Enable Timer                                            | 0       | 1       | 1       | 0       | 1       | 1           | 1         | 1       | 1    | 1     |

| 7                 | DT        | Disable Timer                                           | 0       | 1       | 1       | 0       | 1       | 1           | 1         | 0       | 1    | 1     |

| Control           | ECT       | Enable Counter                                          | 0       | 1       | 1       | 1       | 1       | 1           | 1         | 1       | 1    | 1     |

| ŏ                 | DCT       | Disable Counter                                         | 0       | 1       | 1       | 1       | 1       | 1           | 1         | 0       | 1    | 8 1   |

|                   | HLT       | Halt                                                    | 0       | 1       | 1       | 0       | 1       | 1           | 0         | 1       | 1    | 1     |

|                   | EXP       | Exchange Program                                        | 0       | 1       | 1       | 0       | 1       | 0           | 0         | 1       | 1    | 1     |

|                   | NOP       | No Operation                                            | 0       | 0       | 0       | 0       | 0       | 0           | 0         | 0       | 1    | 1     |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter               | Symbol           | Conditions | Limits      | Unit |

|-------------------------|------------------|------------|-------------|------|

| Supply Voltage          | V <sub>DD</sub>  | Ta = 25°C  | -0.3 to 7   | V    |

| Input Voltage           | VI               | Ta = 25°C  | -0.3 to VDD | V    |

| Operating Voltage PF PG | v <sub>o</sub>   | Ta = 25°C  | -0.3 to 25  | ٧    |

| Storage Temperature     | T <sub>stg</sub> |            | -55 to +150 | °C   |

Note: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING CONDITIONS**

| Parameter             | Symbol          | Conditions | Limits     | Unit |

|-----------------------|-----------------|------------|------------|------|

| County Voltage        | ,,              | @1 MHz     | 3 to 6     | V    |

| Supply Voltage        | V <sub>DD</sub> | @4.2 MHz   | 4.5 to 5.5 | V    |

| Operating Temperature | Top             |            | -40 to +85 | °C   |

| F 0::1                |                 | MOS Load   | 15         |      |

| Fan Out               | N               | TTL Load   | 1          |      |

## D.C. CHARACTERISTICS

$(V_{DD} = 5V \pm 10\%, Ta = -20^{\circ} to +70^{\circ}C)$

| Parameter                          | Symbol            | Conditions                          | Min.  | Тур. | Max. | Unit |

|------------------------------------|-------------------|-------------------------------------|-------|------|------|------|

| High Input Voltage                 | VIH               | _                                   | 3.6   |      |      | ٧    |

| Low input Voltage                  | V <sub>IL</sub>   | _                                   |       |      | 0.8  | V    |

| High Output Voltage (1)            | VOH               | $I_O = -40\mu A$                    | 4.2   |      |      | V    |

| Low Output Voltage                 | V <sub>OL</sub>   | I <sub>O</sub> = 1.6mA              |       |      | 0.4  | V    |

| OSCoInput Leak Current             | l <sub>IH</sub>   | V V 10.1                            |       |      | 25   |      |

| OSC input Leak Current             | IIL               | $V_I = V_{DD/OV}$                   |       |      | -25  | μΑ   |

| RESET, MODE Leak Current           | lн                | VV                                  |       |      | 1    |      |

| NESET, MODE LEAK CUITETI           | IIL               | V <sub>I</sub> = V <sub>DD/OV</sub> |       |      | -50  | μΑ   |

| Input Leak Current <sup>(2)</sup>  | l <sub>I</sub> IH | V. = V = - · · · ·                  |       |      | 1    |      |

| input Leak Current (-/             | IIL               | $V_I = V_{DD/OV}$                   |       | 1    | -1   | μΑ   |

| PA, PB High Output Current         | loн               | V <sub>OH</sub> = 0.4V              |       |      | -1   | mA   |

| High Output Current <sup>(1)</sup> | ЮН                | V <sub>OH</sub> = 2.5V              | -0.25 |      |      | mA   |

| Low Output Current                 | lOL               | V <sub>OL</sub> = 0.4V              | 1.6   |      |      | mA   |

| PF, PG Output Breakdown Voltage    | BVOH              | $I_O = 10\mu A$                     | 20    |      |      | V    |

| Input Capacitance                  | CI                | f = 1 MHz<br>Ta = 25°C              |       | 5    |      | pF   |

| Output Capacitance                 | co                | f = 1 MHz<br>Ta = 25°C              |       | 7    |      | pF   |

|                                    | IDD               | $V_I = V_{DD/OV}$                   |       | 10   | 200  | μΑ   |

| Current Consumption (3)            | IDD               | $V_I = V_{DD/OV}$<br>f = 4.2MHz     |       | 1.6  | 4    | mA   |

Notes: (1) Except PA, PB (see graphs)

(2) Except OSCo, RESET, MODE

(3) Typical Value of V<sub>DD</sub> is 5V

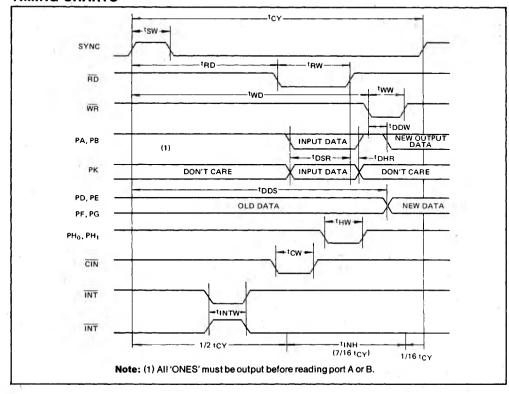

# A.C. CHARACTERISTICS (INTERNAL ROM MODE)

$(V_{DD} = 5V \pm 10\%, Ta = -40^{\circ} to +85^{\circ}C)$

| Parameter                 | Symbol          | Conditions                              | Min.                        | Тур. | Max.                      | Unit |

|---------------------------|-----------------|-----------------------------------------|-----------------------------|------|---------------------------|------|

| CycleTime                 | tcy             |                                         | 7.6                         |      |                           | μS   |

| Sync Pulse Width          | tsw             |                                         | 0.95                        |      |                           | μS   |

| RD Pulse Width            | tRW             |                                         | 1.9                         |      |                           | μS   |

| Sync † to RD ↓            | t <sub>RD</sub> | C <sub>L</sub> = 50pF                   | 1/2 t <sub>CY</sub> + 0.5   |      |                           | μS   |

| WR Pulse Width            | tww             |                                         | 0.95                        |      |                           | μS   |

| Sync † to WR ↓            | twp             | C <sub>L</sub> = 50pF                   | 13/16 t <sub>CY</sub> + 0.5 |      |                           | μS   |

| Port Input Setup Time     | tDSR            |                                         | 4/16 t <sub>CY</sub>        |      | 7                         | μS   |

| Port Input Hold Time      | tDHR            |                                         | 0                           |      | 0.8                       | μS   |

| WR   to New Data Valid    | tDDW            | PA, PB<br>C <sub>L</sub> = 50pF         |                             |      | 0.8                       | μS   |

| Sync † to New Data Valid  | tDDS            | PD, PE, PF, PG<br>C <sub>L</sub> = 50pF |                             |      | 13/16 t <sub>CY+0.5</sub> | μS   |

| PHo, PH Input Pulse Width | tHW             | (1)                                     | 500                         |      |                           | nS   |

| CIN Input Pulse Width     | tcw             |                                         | 250                         |      |                           | nS   |

| INT Input Pulse Width     | tINTW           | (1)                                     | 500                         |      |                           | nS   |

Note: (1) The processor logic will ignore the following events:

- 1. An INT falling edge occurring during TINH of a Ti instruction.

- 2. A PHo or PHolow level occurring only during TINH of a THB instruction.

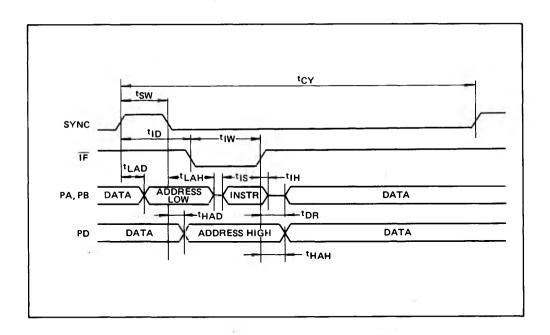

### **TIMING CHARTS**

# A.C. CHARACTERISTICS (EXTERNAL ROM MODE)

$(V_{DD} = 5V \pm 10\%, Ta = -40^{\circ} \text{ to } +85^{\circ}\text{C})$

| Parameter          | Symbol          | Conditions            | Min.                 | Тур. | Max.                   | Unit |

|--------------------|-----------------|-----------------------|----------------------|------|------------------------|------|

| CycleTime          | tcy             |                       | 7.6                  |      | Ξ                      | μS   |

| Sync Pulse Width   | tsw             |                       | 0.95                 |      |                        | μS   |

| ĪF Pulse Width     | tıw             |                       | 1.425                |      | -                      | μS   |

| Sync † to ÎF ↓     | t <sub>ID</sub> | C <sub>L</sub> = 50pF | 3/16 tcy + 1         |      |                        | μS   |

| Address Low Delay  | tLAD            | C <sub>L</sub> = 50pF |                      |      | 0.8                    | μS   |

| Address Low Hold   | tLAH            | ¢-                    | 1/16 t <sub>CY</sub> |      | 1/16 t <sub>CY+1</sub> | μS   |

| Instruction Setup  | tıs             |                       | 1/16 t <sub>CY</sub> |      |                        | μS   |

| Instruction Hold   | tiH             |                       |                      |      | 20                     | nS   |

| Data Recovery      | t <sub>DR</sub> | C <sub>L</sub> = 50pF | 0                    |      | 0.8                    | μS   |

| Address High Delay | tHAD            | C <sub>L</sub> = 50pF |                      |      | 0.5                    | μS   |

| Address High Hold  | tHAH            |                       | 0                    |      | 0.5                    | μS   |

| Cycle Dependent Timings | 4MHz   | 2MHz | 1 MHz | 500kHz |

|-------------------------|--------|------|-------|--------|

| 1/16t <sub>CY</sub>     | 0.5μS  | 1μS  | 2μS   | 4μS    |

| 1/16t <sub>CY+1</sub>   | 1.5μS  | 2μ\$ | 3μS   | 5μS    |

| 3/16t <sub>CY+1</sub>   | 2.5μ\$ | 4μS  | 7μS   | 13µS   |

| 4/16t <sub>CY-1</sub>   | 1μS    | 3μS  | 7μS   | 15μS   |

| 1/2t <sub>CY+1</sub>    | 5μS    | 9μS  | 17μS  | 33µS   |

| 7/16t <sub>CY</sub>     | 3.5μS  | 7μS  | 14μS  | 28µS   |

| 13/16t <sub>CY+1</sub>  | 7.5µS  | 14µS | 27μS  | 53μS   |

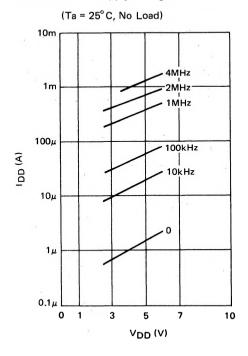

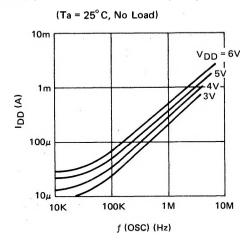

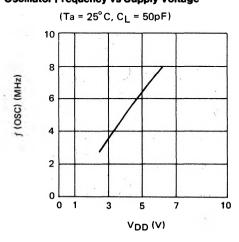

# TYPICAL PERFORMANCE CURVES

# **Supply Current vs Supply Voltage**

# **Supply Current vs Oscillator Frequency**

# Oscillator Frequency vs Supply Voltage

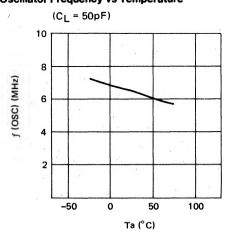

# **Oscillator Frequency vs Temperature**

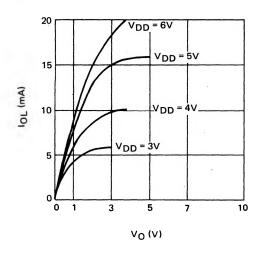

# **Low Current Out vs Voltage**

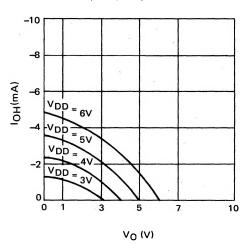

### **High Current Out vs Voltage**

(Ta = 25°C, Except PA, PB)

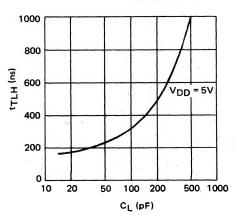

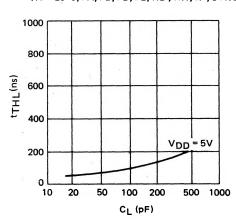

### Fall Time vs Load

(Ta = 25°C, PA, PB, PD, PE, RD, WR, IF, SYNC)

#### Rise Time vs Load

(Ta = 25°C, PD, PE, RD, WR, IF, SYNC)