19-0936; Rev 1; 7/95

## CMOS 10 and 12 Bit **Multiplying D/A Converters**

#### **General Description**

The MX7520 and MX7521 are low cost CMOS multi-plying digital-to-analog converters (DACs) with 10 and 12 bit resolution respectively. Both DACs operate from a +5V to +15V supply and dissipate only 20mW.

Thin-film resistors provide typically 0.3% untrimmed gain error and 10ppm/°C gain temperature coeffi-cient. All digital inputs are compatible with both CMOS and TTL logic levels.

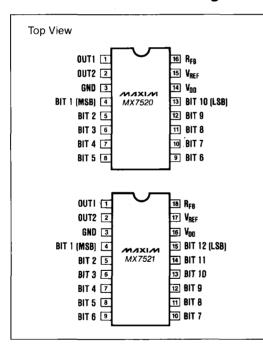

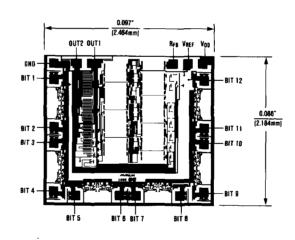

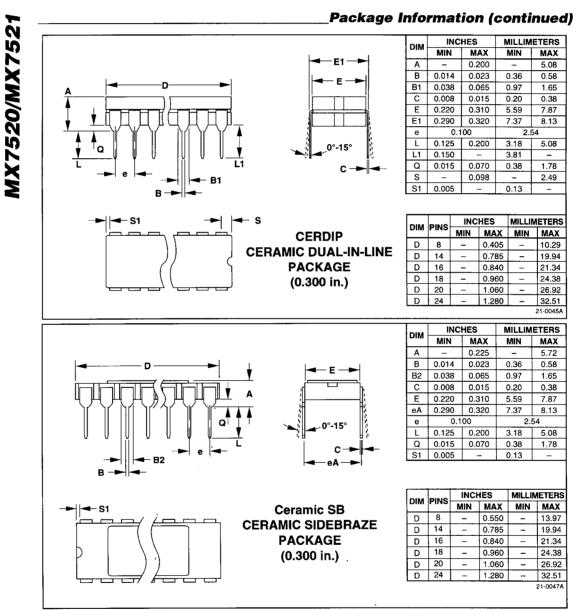

Maxim's MX7520 and MX7521 are electrically and pin compatible with Analog Devices' AD7520 and AD7521. The MX7520 is packaged in a 16-lead DIP while the MX7521 is packaged in an 18-lead DIP. Both devices are also available in small outline (SO) packages.

#### **Applications**

- Machine and Motion Control Systems

- Automatic Test Equipment

- µP Controlled Calibration Circuitry

- Programmable Gain Amplifiers

- **Digitally Controlled Filters**

- **Programmable Power Supplies**

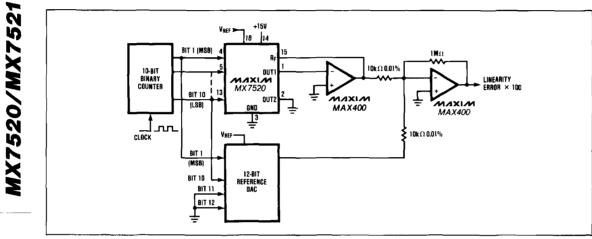

#### Pin Configuration

### Features

MX7520/MX7521

- 10 or 12 Bit Resolution ٠

- ۲ 8, 9, and 10 Bit End Point Linearity

- ♦ Low Power Consumption 20mW

- TTL and CMOS Compatible ۲

- Pin-For-Pin Second Source

#### **Ordering Information**

| PART       | TEMP. RANGE     | PACKAGE*      | ERROR |

|------------|-----------------|---------------|-------|

| MX7520JN   | 0°C to +70°C    | Plastic DIP   | 0.2%  |

| MX7520KN   | 0°C to +70°C    | Plastic DIP   | 0.1%  |

| MX7520LN   | 0°C to +70°C    | Plastic DIP   | 0.05% |

| MX7520JCWE | 0°C to +70°C    | Small Outline | 0.2%  |

| MX7520KCWE | 0°C to +70°C    | Small Outline | 0.1%  |

| MX7520LCWE | 0°C to +70°C    | Small Outline | 0.05% |

| MX7520J/D  | 0°C to +70°C    | Dice          | 0.2%  |

| MX7520JQ   | -25°C to +85°C  | CERDIP**      | 0.2%  |

| MX7520KQ   | -25°C to +85°C  | CERDIP**      | 0.1%  |

| MX7520LQ   | -25°C to +85°C  | CERDIP**      | 0.05% |

| MX7520JD   | -25°C to +85°C  | Ceramic       | 0.2%  |

| MX7520KD   | -25°C to +85°C  | Ceramic       | 0.1%  |

| MX7520LD   | -25°C to +85°C  | Ceramic       | 0.05% |

| MX7520SQ   | -55°C to +125°C | CERDIP**      | 0.2%  |

| MX7520TQ   | -55°C to +125°C | CERDIP**      | 0.1%  |

| MX7520UQ   | -55°C to +125°C | CERDIP**      | 0.05% |

| MX7520SD   | -55°C to +125°C | Ceramic       | 0.2%  |

| MX7520TD   | -55°C to +125°C | Ceramic       | 0.1%  |

| MX7520UD   | -55°C to +125°C | Ceramic       | 0.05% |

\*\* Maxim reserves the right to ship Ceramic packages in lieu of

CERDIP packages. Ordering Information continued on last page.

#### **Typical Operating Circuit**

Maxim Integrated Products 1

## **WIXIW**

1-800-998-8800 for fr es or literature.

### ABSOLUTE MAXIMUM RATINGS

| V <sub>DD</sub> to GND                              | Operatin |

|-----------------------------------------------------|----------|

| V <sub>REF</sub> to GND ±25V                        | Comm     |

| R <sub>FB</sub> to GND ±25V                         | Indust   |

| Digital Input Voltage to GND                        | Militar  |

| Output Voltage (OUT1, OUT2) (Note 1)0.3V, VDD       | Storage  |

| Power Dissipation (Derate 6mW/°C above +75°C) 450mW | Lead Ter |

| Operating Temperature                |                |

|--------------------------------------|----------------|

| Commercial (JN/KN/LN/JC/KC/LC)       | 0°C to +70°C   |

| Industrial (JD/KD/LD/JQ/KQ/LQ)       | 25°C to +85°C  |

| Military (S/T/U)                     | 55°C to +125°C |

| Storage Temperature                  | 65°C to +150°C |

| Lead Temperature (Soldering 10 secs) | +300°C         |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

MX7520/MX7521

ELECTRICAL CHARACTERISTICS (T<sub>A</sub>=+25°C, V<sub>DD</sub> =+ 15V, V<sub>REF</sub> = +10V, V<sub>OUT1</sub> = V<sub>OUT2</sub> = GND, unless otherwise specified)

| PARAMETER                                | SYMBOL             | CONDITIONS                                                                                                                                                                                                                                                         | MIN.      | TYP.                   | MAX.                  | UNITS                    |

|------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|-----------------------|--------------------------|

| DC ACCURACY (Note 2)                     |                    |                                                                                                                                                                                                                                                                    |           |                        |                       |                          |

| Resolution                               |                    | MX7520<br>MX7521                                                                                                                                                                                                                                                   | 10<br>12  |                        |                       | Bits                     |

| Relative Accuracy (Note 3)               |                    | $\label{eq:relation} \begin{array}{ll} -10V \leq V_{REF} \leq +10V, \\ T_A = T_{MIN} \mbox{ to } T_{MAX} \end{array} \qquad \begin{array}{ll} 0.2\% \mbox{ FSR = 8 Bits } J/S \\ 0.1\% \mbox{ FSR = 9 Bits } K/T \\ 0.05\% \mbox{ FSR = 10 Bits } L/U \end{array}$ |           |                        | ±0.2<br>±0.1<br>±0.05 | % FSR                    |

| Nonlinearity Tempco                      |                    | -10V ≤ V <sub>REF</sub> ≤ +10V (Note 4)                                                                                                                                                                                                                            |           |                        | 2                     | ppm/°C                   |

| Gain Error                               |                    | -10V ≤ V <sub>REF</sub> ≤ +10V (Note 5)                                                                                                                                                                                                                            |           | 0.3                    |                       | % FSR                    |

| Gain Error Tempco                        |                    | -10V ≤ V <sub>REF</sub> ≤ +10V (Note 4,5)                                                                                                                                                                                                                          |           |                        | 10                    | ppm/°C                   |

| Output Leakage Current                   |                    | OUT1 or OUT2, T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                                                                                |           | 200                    |                       | nA                       |

| Power Supply Rejection                   | PSRR               | (Note 3)                                                                                                                                                                                                                                                           |           | 50                     |                       | ppm/<br>%V <sub>DD</sub> |

| V <sub>REF</sub> Input Resistance        | RREF               | R <sub>REF</sub> tempco = -150ppm/°C typ.                                                                                                                                                                                                                          | 5         | 10                     | 20                    | kΩ                       |

| AC ACCURACY                              |                    |                                                                                                                                                                                                                                                                    |           |                        |                       |                          |

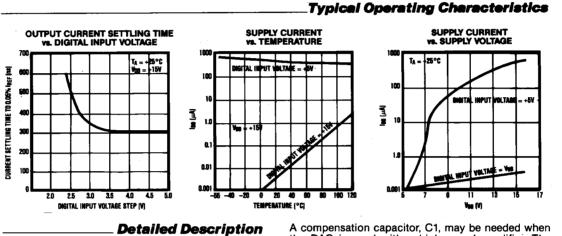

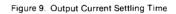

| Output Current Settling Time<br>(Note 3) |                    | To 0.05% of FSR, all digital inputs<br>high to low and low to high.                                                                                                                                                                                                |           | 500                    |                       | ns                       |

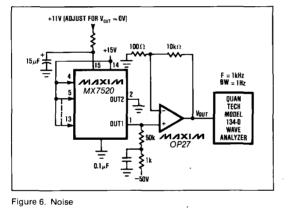

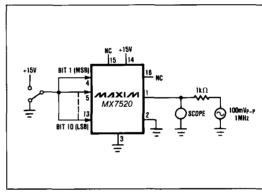

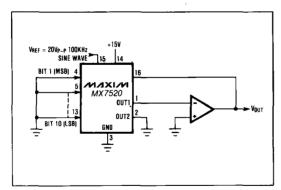

| Feedthrough Error<br>(Note 3,4,6)        |                    | All digital inputs low, V <sub>REF</sub> = 20V <sub>P-P</sub> ,<br>100kHz sinewave.                                                                                                                                                                                |           | 10                     |                       | mV <sub>P-P</sub>        |

| ANALOG OUTPUTS                           |                    | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                              |           |                        |                       |                          |

| Output Capacitance (Note 3)              | Солт               | All digital inputs high, OUT1<br>All digital inputs low, OUT2<br>All digital inputs low, OUT2                                                                                                                                                                      |           | 120<br>37<br>37<br>120 |                       | pF                       |

| Output Noise (Note 3)                    | e <sub>N</sub>     | Both outputs, equivalent Johnson noise resistance                                                                                                                                                                                                                  |           |                        | 10                    | kΩ                       |

| DIGITAL INPUTS (TA = TMIN to             | T <sub>MAX</sub> ) |                                                                                                                                                                                                                                                                    |           |                        |                       |                          |

| Low State Threshold                      | VINL               |                                                                                                                                                                                                                                                                    |           |                        | 0.8                   | v                        |

| High State Threshold                     | VINH               |                                                                                                                                                                                                                                                                    | 2.4       |                        |                       | v                        |

| Input Current                            |                    | Low to high state                                                                                                                                                                                                                                                  |           | ±1                     |                       | μA                       |

| Input Coding                             |                    | Unipolar (Table 1), Bipolar (Table 2)                                                                                                                                                                                                                              | Binary, O | ffset Bina             | ry                    |                          |

| POWER REQUIREMENTS                       |                    |                                                                                                                                                                                                                                                                    |           |                        |                       |                          |

| Power Supply Range                       | V <sub>DD</sub>    |                                                                                                                                                                                                                                                                    | +5        |                        | +15                   | v                        |

| Power Supply Current                     | IDO                | Digital inputs at GND<br>Digital inputs high or low                                                                                                                                                                                                                |           | 5                      | 2                     | nA<br>mA                 |

| Total Power Dissipation                  |                    | Including V <sub>REF</sub>                                                                                                                                                                                                                                         |           | 20                     |                       | mW                       |

2 \_\_

Note 1: V<sub>OUT1/2</sub> may exceed the Absolute Maximum voltage if the current is limited to 30mA or less.

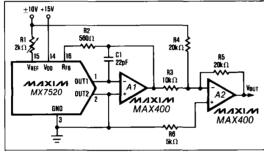

Note 3: See Test Circuits.

Note 4: Guaranteed by design but not 100% tested.

Note 5: To minimize feedthrough with the ceramic package, the metal lid must be grounded. If the lid is not grounded, then the feed-through is 10mV typical and 30mV maximum.

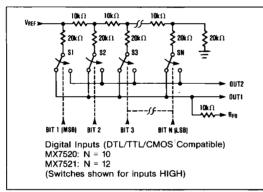

The basic MX7520/21 DAC circuit consists of a lasertrimmed, thin-film R-2R resistor array with CMOS current switches as shown in Figure 1. Binarily weighted currents are switched to either OUT1 or OUT2 depending on the status of each input bit. The V<sub>REF</sub> input accepts a wide range of reference signals including fixed and time-varying voltage or current inputs.

Figure 1. MX7520/MX7521 Functional Diagram

## Application Information

Unipolar Operation

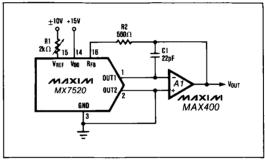

The most common configuration for the MX7520/21 is shown in Figure 2. The circuit is used for unipolar binary operation and/or 2-quadrant multiplication. R1 is used for gain adjustment. If no adjustment is desired, R1 and R2 can be omitted. The code table for unipolar operation is given in Table 1. Note that the output polarity is the inverse of the reference input.

A compensation capacitor, C1, may be needed when the DAC is used with a high speed amplifier. The purpose of the capacitor is to cancel the pole formed by the DAC's output capacitance and internal feedback resistance. The correct compensation value depends on the type of op-amp used but typically ranges from 10 to 50pF.

Figure 2. Unipolar Binary Operation (2-Quadrant Multiplication)

#### Table 1: Code Table (MX7520) — Unipolar Binary Operation

|   |   | -   |   |   |     |      |     | -  |               |   |                                           |

|---|---|-----|---|---|-----|------|-----|----|---------------|---|-------------------------------------------|

|   |   |     | D | G | TAI | L IN | IPL | JT | ANALOG OUTPUT |   |                                           |

| ļ | 1 | 1   | 1 | 1 | 1   | 1    | 1   | 1  | 1             | 1 | -V <sub>REF</sub> (1 - 2 <sup>-10</sup> ) |

| i | 1 | · 0 | 0 | 0 | 0   | 0    | 0   | 0  | 0             | 1 | -V <sub>REF</sub> (½ + 2 <sup>-10</sup> ) |

|   | 1 | 0   | 0 | 0 | 0   | 0    | 0   | 0  | 0             | 0 | -V <sub>REF</sub> /2                      |

|   | 0 | 1   | 1 | 1 | 1   | 1    | 1   | 1  | 1             | 1 | -V <sub>REF</sub> (½ - 2 <sup>-10</sup> ) |

|   | 0 | 0   | 0 | 0 | 0   | 0    | 0   | 0  | 0             | 1 | -V <sub>REF</sub> (2 <sup>-10</sup> )     |

|   | 0 | 0   | 0 | 0 | 0   | 0    | 0   | 0  | 0             | 0 | 0                                         |

Note: 1 LSB = 2<sup>-10</sup> V<sub>BEF</sub> (MX7520)

M/X/M

MX7520/MX7521

MX7520/MX7521

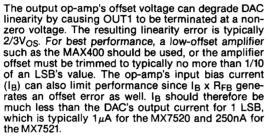

Figure 3. Bipolar Operation (4-Quadrant Multiplication)

#### Table 2: Code Table (MX7520) — Bipolar (Offset Binary) Operation

| - |   |   | •   | _  |     |     |    |               |   |                                          |

|---|---|---|-----|----|-----|-----|----|---------------|---|------------------------------------------|

|   |   | D | IGI | TA | LIN | IPL | JT | ANALOG OUTPUT |   |                                          |

| 1 | 1 | 1 | 1   | 1  | 1   | 1   | 1  | 1             | 1 | -V <sub>REF</sub> (1 - 2 <sup>-9</sup> ) |

| 1 | 0 | 0 | 0   | 0  | 0   | 0   | 0  | 0             | 1 | -V <sub>REF</sub> (2 <sup>-9</sup> )     |

| 1 | 0 | 0 | 0   | 0  | 0   | 0   | 0  | 0             | 0 | 0                                        |

| 0 | 1 | 1 | 1   | 1  | 1   | 1   | 1  | 1             | 1 | V <sub>REF</sub> (2 <sup>-9</sup> )      |

| 0 | 0 | 0 | 0   | 0  | 0   | 0   | 0  | 0             | 1 | V <sub>REF</sub> (1 - 2 <sup>-9</sup> )  |

| 0 | 0 | 0 | 0   | 0  | 0   | 0   | 0  | 0             | 0 | V <sub>REF</sub>                         |

|   |   |   |     |    |     |     |    |               |   | · · · · · · · · · · · · · · · · · · ·    |

Note: 1 LSB = 2<sup>-9</sup> V<sub>REF</sub> (MX7520)

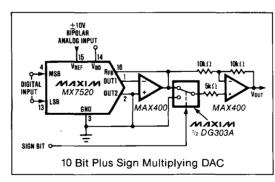

#### **Bipolar Operation**

Bipolar, or four-quadrant, operation is shown in Figure 3. A second amplifier and three matched resistors are required. The output vs. code table is listed in Table 2. In multiplying applications, the MSB determines polarity while the remaining bits control amplitude.

To adjust the circuit, load the DAC with a code of 1000 0000 0000 and trim R1 for a 0V output. With R1 and R2 omitted, an alternative zero trim is to adjust the ratio of R3 and R4 for 0V out. Full scale can be trimmed by loading the DAC with all "zeros" or all "ones" and adjusting the amplitude of  $V_{\text{REF}}$  or varying R5 until the desired positive or negative output is obtained. The op-amp recommendations made in the Unipolar Operation section apply for bipolar operation as well.

#### Voltage Mode (Single Supply)

The MX7520 is connected as a voltage output DAC in Figure 4. OUT1 is connected to the external reference and OUT2 is grounded. V<sub>REF</sub>, now the DAC output, is a voltage source with a constant output resistance of R<sub>ladder</sub> (nominally 10kΩ). In most circuits this output is buffered with an op-amp.

Figure 4. Single Supply Voltage Mode Operation

An advantage of voltage mode operation is single supply operation for the complete circuit, i.e. a negative reference is not required for a positive output. It is important to note that the range of the reference is restricted. The reference input (voltage at OUT1) must always be positive and is limited to no more than 3.5V when  $V_{DD}$  is 15V. If the reference voltage is greater than 3.5V, or  $V_{DD}$  is reduced, linearity is degraded.

#### **Dynamic Considerations**

In static or DC applications, the AC characteristics of the output amplifier are not critical. In higher speed applications, where either the reference input is an AC signal or the DAC output must quickly settle to a new programmed value, the AC parameters of the output op-amp must be considered.

Another error source in dynamic applications is parasitic coupling of signal from the  $V_{REF}$  terminal to OUT1 or OUT2. This is normally a function of board layout and package lead-to-lead capacitance. Signals can also be injected into the DAC outputs when the digital inputs are switched. This digital feedthrough is mostly dependent on circuit board layout and on-chip capacitive coupling. Layout induced feedthrough can be minimized with guard traces between digital inputs, V<sub>REF</sub>, and the DAC outputs.

Figure 5. Power Supply Rejection

,

VREF

MX7520 0UT1

GND

<u>\_</u>3

OUT

Figure 7. Output Capacitance

BIT 1 (MSB)

BIT 10 (LSB)

///XI//I

+100mV

100Ω

Figure 10. Relative Accuracy

#### Ordering Information (continued)

| PART       | TEMP. RANGE     | PACKAGE*      | ERROR |

|------------|-----------------|---------------|-------|

| MX7521JN   | 0°C to +70°C    | Plastic DIP   | 0.2%  |

| MX7521KN   | 0°C to +70°C    | Plastic DIP   | 0.1%  |

| MX7521LN   | 0°C to +70°C    | Plastic DIP   | 0.05% |

| MX7521JCWN | 0°C to +70°C    | Small Outline | 0.2%  |

| MX7521KCWN | 0°C to +70°C    | Small Outline | 0.1%  |

| MX7521LCWN | 0°C to +70°C    | Small Outline | 0.05% |

| MX7521J/D  | 0°C to +70°C    | Dice          | 0.2%  |

| MX7521JQ   | -25°C to +85°C  | CERDIP"       | 0.2%  |

| MX7521KQ   | -25°C to +85°C  | CEBDIP**      | 0.1%  |

| MX7521LQ   | -25°C to +85°C  | CERDIP**      | 0.05% |

| MX7521JD   | -25°C to +85°C  | Ceramic       | 0.2%  |

| MX7521KD   | -25°C to +85°C  | Ceramic       | 0.1%  |

| MX7521LD   | -25°C to +85°C  | Ceramic       | 0.05% |

| MX7521SQ   | -55°C to +125°C | CERDIP**      | 0.2%  |

| MX7521TQ   | -55°C to +125°C | CERDIP**      | 0.1%  |

| MX7521UQ   | -55°C to +125°C | CERDIP**      | 0.05% |

| MX7521SD   | -55°C to'+125°C | Ceramic       | 0.2%  |

| MX7521TD   | -55°C to +125°C | Ceramic       | 0.1%  |

| MX7521UD   | -55°C to +125°C | Ceramic       | 0.05% |

MX7520 — 16 lead package, MX7521 — 18 lead package.

\*\* Maxim reserves the right to ship Ceramic packages in lieu of CERDIP packages.

6

**WIXIW**

####

7

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

8

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1995 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Products.