## **High-Efficiency Inverter Controller**

### **FEATURES**

- Single-stage power conversion, requiring only a +5 V voltage source

- Reduces the number of components and board size by 30% compared with conventional design

- Supports both floating and grounded secondary designs

- 90% efficiency vs. typical 75% efficiency of conventional designs

- Internal open-lamp and short-circuit protections

- · Wide dimming range

- Supports multiple CCFLs

- Simple and reliable 2-winding transformer design

- Eliminates leakage current when used in a floating secondary design

- Constant-frequency design eliminates interference with LCDs

#### ORDERING INFORMATION

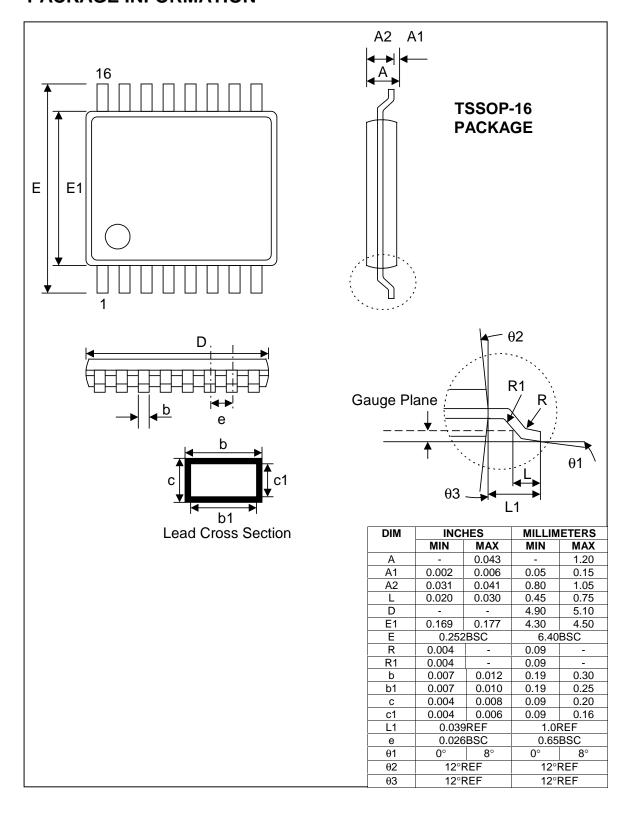

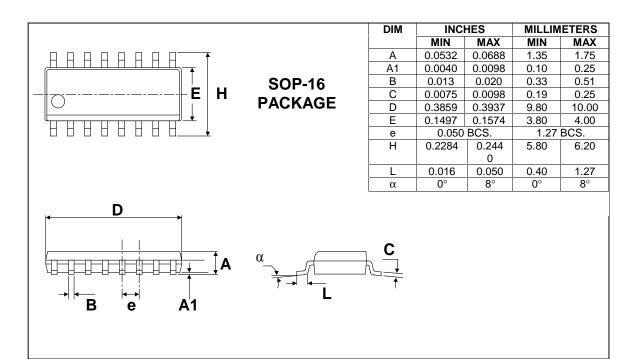

OZ965G - 16-pin plastic SOP OZ965R - 16-pin plastic TSSOP OZ965IG - 16-pin plastic SOP OZ965IR - 16-pin plastic TSSOP

### **GENERAL DESCRIPTION**

The OZ965 is a single chip, high-efficiency, Cold Cathode Fluorescent Lamp (CCFL) backlight inverter controller whose primary function is to convert +5 volt DC power to approximately 600 VAC. Additionally, the OZ965 performs the lamp

dimming function with an analog voltage or low frequency Pulse Width Modulation (PWM) control.

#### Operating Principle:

The CCFL tube, transformer secondary, and capacitor form a resonant circuit. The OZ965 utilizes the low energy loss resonate mode principle to deliver a very high efficiency inverter.

The OZ965 drives the transformer primary with a variable pulse width voltage directly from the +5v supply. The resultant primary drive current is alternately reversing with zero-voltage-switching. Because of the transformer leakage inductance and the secondary resonant circuit, the secondary voltage and current are approximately sinusoidal. This sinusoid results in very little harmonic emi/rfi emissions.

The OZ965 operates at a single, constant frequency in a PWM mode. Typical operating frequency ranges between 30 KHz to 200 KHz, dependent upon the CCFL and transformer characteristics. Intelligent open-lamp protection provides design flexibility so various transformer models/manufacturers may be used.

Its high driving capability allows the OZ965 to drive high power MOSFETs.

The single stage design results in a low cost, reliable transformer without expensive, less reliable secondary fold-back treatment. The transformer does not require a more expensive center tapped primary.

The OZ965 is available in 16-pin SOP and TSSOP packages. It is specified over the commercial temperature range of 0°C to +70°C, and the industrial temperature range of -40°C to +85°C.

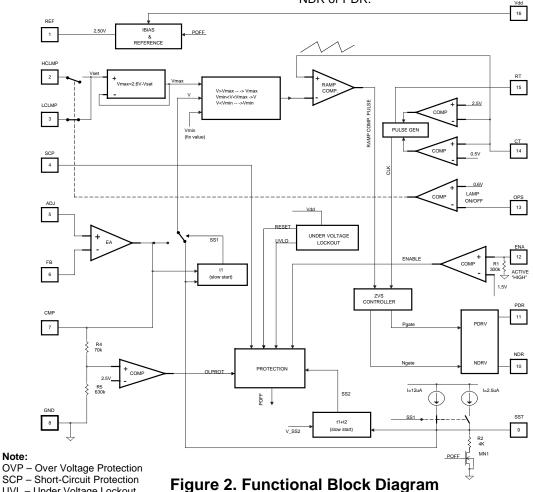

### **FUNCTIONAL BLOCK DIAGRAM**

Refer to the functional block diagram in Figure 2, below, and the Pin Description Table on page 3.

Power is transferred to the transformer primary by the N-MOSFET, driven by the MOSFET gate driver out of pin NDR. The P-MOSFET resets the primary field, driven by pin PDR. The usual design results in approximately 50% duty cycle at full lamp intensity. Terminating the NDR signal earlier than the full brightness lamp pulse width performs lamp dimming, using the analog dimming. The voltages on pins HCLMP and LCLMP set a threshold voltage for the ramp comparator setting the maximum duty cycle for NDR.

A pulse generator circuit creates the clock signal with the frequency determined by an external, constant current setting resistor (RT) and timing capacitor (CT).

The "soft-start" circuit ensures a reliable and long lamp life starting condition.

UVL - Under Voltage Lockout

"Soft start" gradually increases the energy delivered to the secondary.

When the OZ965 is enabled at pin ENA, the capacitor on pin SST determines the duration of the "soft-start" period, gradually increasing the NDR pulse width to the regulated brightness. The "soft-start" period provides sufficient time for the lamp to ignite.

For system reliability there are several circuit protections provided. To ensure a controlled output, the secondary current is monitored on pin FB and is compared to a reference voltage on pin ADJ. The NDR signal is shortened or lengthened dependent upon this feedback. Protection is provided by the resultant signal, CMP, monitoring for a lamp removal condition. Short circuit protection is provided at pin SCP. The OPS signal selects either HCLMP or LCLMP providing current protection against an "Open Lamp" condition at start-up. The OPS signal also allows adjustment to different transformer models.

To reduce power dissipation, the switch (MOSFET) drive signals are "break-before-make" with a short, fixed off time between activation of NDR or PDR.

## **PIN DESCRIPTION**

| Names | Pin No. | I/O | Description                                                                    |  |  |  |

|-------|---------|-----|--------------------------------------------------------------------------------|--|--|--|

| REF   | 1       | 0   | Reference voltage output. Nominal voltage is 2.5 V.                            |  |  |  |

| HCLMP | 2       | ı   | Clamping maximum duty cycle under normal operation.                            |  |  |  |

| LCLMP | 3       |     | Clamping maximum duty cycle under open-lamp condition.                         |  |  |  |

| SCP   | 4       | ı   | Short-circuit protection input (V <sub>TH</sub> =0.6V)                         |  |  |  |

| ADJ   | 5       |     | Reference voltage input for dimming control.                                   |  |  |  |

| FB    | 6       | I   | Current sense feedback.                                                        |  |  |  |

| CMP   | 7       | 0   | Compensation for the current sense feedback.                                   |  |  |  |

| GND   | 8       | GND | Ground.                                                                        |  |  |  |

| SST   | 9       | I   | Soft-start ensures lamp current pulses gradually increases to its normal value |  |  |  |

| PDR   | 10      | 0   | Gate drive output for the P-MOSFET.                                            |  |  |  |

| NDR   | 11      | 0   | Gate drive output for the N-MOSFET.                                            |  |  |  |

| ENA   | 12      |     | Enable input, active high (V <sub>TH</sub> =1.5V)                              |  |  |  |

| OPS   | 13      | I   | Output current sense (V <sub>TH</sub> =0.6V)                                   |  |  |  |

| CT    | 14      | I/O | Timing capacitor. CT and RT set the clock frequency.                           |  |  |  |

| RT    | 15      | I/O | Timing resistor. Fosc = 1.91 / (Rt • Ct)                                       |  |  |  |

| VDD   | 16      | PWR | Supply voltage input.                                                          |  |  |  |

### **ABSOLUTE MAXIMUM RATINGS**

| VDD          | 5.5V               |

|--------------|--------------------|

| GND          | +/- 0.3V           |

| Logic inputs | -0.3 V to VDD+0.3V |

|                 | OZ965       | OZ965I        |

|-----------------|-------------|---------------|

| Operating temp. | 0°C to 70°C | -40°C to 85°C |

| Operating junction temp. | 150°C          |

|--------------------------|----------------|

| Storage temp.            | -55°C to 150°C |

|                                               | OZ965              | OZ965I             |

|-----------------------------------------------|--------------------|--------------------|

| Power dissipation - 16-pin SOP - 16-pin TSSOP | .720W<br>.690W     | .580W<br>.550W     |

| Thermal Impedance - 16-pin SOP - 16-pin TSSOP | 111°C/W<br>115°C/W | 111°C/W<br>115°C/W |

### RECOMMENDED OPERATING RANGE

| VDD  | 5.0 V +/- 5%      |

|------|-------------------|

| Fosc | 30 KHz to 200 KHz |

| Rosc | 50 k to 150 k     |

## **FUNCTIONAL SPECIFICATIONS**

| Parameter                        | Symbol                                              | Test Conditions                                |      | Limits  | <u> </u>    | Unit   |

|----------------------------------|-----------------------------------------------------|------------------------------------------------|------|---------|-------------|--------|

|                                  |                                                     | 4.75 V < VDD < 5.25 V                          | Min  | Тур     | Max         |        |

| Reference Voltage                |                                                     |                                                |      |         |             |        |

| Nominal voltage                  | Vref                                                | $I_{load} = 0.1 \text{ mA},$                   | 2.37 | 2.50    | 2.63        | V      |

| Line regulation                  |                                                     |                                                | -    | 6       | -           | mV/V   |

| Load regulation                  |                                                     | $I_{load} = 0.2 \text{ mA to } 1.0 \text{ mA}$ | -    | 1       | -           | mV/mA  |

| Oscillator                       |                                                     |                                                |      |         |             |        |

| Initial accuracy                 | fosc                                                | Ct = 470 pF, Rt = 49.9 k                       |      | 81      |             | KHz    |

| Ramp peak                        |                                                     |                                                | -    | 2.54    | -           | V      |

| Ramp valley                      |                                                     |                                                | -    | 0.48    | -           | V      |

| Temp. stability                  |                                                     | $TA = -40^{\circ}C \text{ to } 85^{\circ}C$    | -    | -       | 200         | ppm/°C |

| Error Amplifier                  |                                                     |                                                |      |         |             |        |

| Input bias current               |                                                     | ADJ=FB=2.0 V                                   | -    | 0.25    | -           | uA     |

| Input offset voltage             |                                                     | VFB = 4.0 V                                    |      | 5       | 10          | mV     |

| Input voltage range              |                                                     |                                                | 0    | -       | VDD-<br>1.5 | V      |

| Open loop voltage gain           |                                                     |                                                | -    | 65      | -           | dB     |

| Unity gain bandwidth             |                                                     |                                                | -    | 1.5     | -           | MHz    |

| Power supply rejection           |                                                     |                                                | -    | 60      | -           | dB     |

| Under-Voltage Lockout            |                                                     |                                                |      |         |             |        |

| Positive-going threshold voltage | ositive-going threshold voltage See Table 1, page 5 |                                                |      |         |             |        |

| Negative-going threshold voltage |                                                     |                                                | See  | Table 1 | , page 5    |        |

| Supply                           |                                                     |                                                |      |         |             |        |

| Supply current - Enable Low      | I <sub>OFF</sub>                                    |                                                | -    | 195     | -           | μΑ     |

| Supply current - Enable High     | I <sub>ON</sub>                                     | VDD = 5.0 V                                    | -    | 1.0     | -           | mA     |

| NDR output                       |                                                     |                                                |      |         |             |        |

| Output high voltage              | V <sub>OH</sub>                                     | Isource = 10 mA, VDD = 5V                      | -    | 4.75    | -           | V      |

| Output low voltage               | V <sub>OL</sub>                                     | Isink = 10 mA, VDD = 5V                        | -    | 0.25    | 0.5         | V      |

| Output resistance                | R <sub>OUT</sub>                                    |                                                | -    | 10      | -           | Ω      |

| PDR output                       |                                                     |                                                |      |         |             |        |

| Output high voltage              | V <sub>OH</sub>                                     | Isource = 10 mA, VDD = 5V                      | -    | 4.7     | -           | V      |

| Output low voltage               | V <sub>OL</sub>                                     | Isink = 10 mA, VDD = 5V                        | -    | 0.5     | -           | V      |

| Output resistance                | R <sub>OUT</sub>                                    |                                                | -    | 15      |             | Ω      |

| Break-Before-Make                |                                                     |                                                |      |         |             |        |

| Qn off to Qp on delay            | T <sub>HL</sub>                                     |                                                | -    | 250     | -           | ns     |

| Qp off to Qn on delay            | T <sub>LH</sub>                                     |                                                | -    | 220     | -           | Ns     |

| High Clamp                       |                                                     |                                                |      |         |             |        |

| Duty cycle of NDR                | HCLMP                                               | OPS=1 V V <sub>HCLMP</sub> =0V                 | 92   | 94      | 96          | %      |

|                                  |                                                     | OPS=1 V, V <sub>HCLMP</sub> =1.8V              | -    | 14      | -           | 1      |

| Low Clamp                        |                                                     |                                                |      |         |             |        |

| Duty cycle of NDR                | LCLMP                                               | OPS=0 V, V <sub>LCLMP</sub> =0V                | 92   | 94      | 96          | %      |

|                                  |                                                     | OPS=0 V, V <sub>LCLMP</sub> =1.8V              | -    | 14      | -           | ]      |

| Max. / Min. Duty cycle           |                                                     |                                                |      |         |             |        |

| Duty cycle of NDR                |                                                     |                                                | 6    | -       | 95          | %      |

|                                  | I                                                   | 1                                              |      | L       | <u> </u>    |        |

|                                  | OZ965               |     |        |     |      |     | OZ965I |     |      |

|----------------------------------|---------------------|-----|--------|-----|------|-----|--------|-----|------|

| Parameter                        | Test Conditions     |     | Limits |     | Unit |     | Limits |     | Unit |

|                                  | 4.75V < VDD < 5.25V | Min | Тур    | Max |      | Min | Тур    | Max |      |

| Under-Voltage Lockout            |                     |     |        |     |      |     |        |     |      |

| Positive-going threshold voltage |                     | -   | 3.9    | 4.3 | V    | -   | 3.9    | 4.5 | V    |

| Negative-going threshold voltage |                     | 3.2 | 3.4    | -   | V    | 3.0 | 3.4    | -   | V    |

Table 1. Under-Voltage Lockout for OZ965 and OZ965I

#### **FUNCTIONAL INFORMATION**

### 1. Steady-State Operation

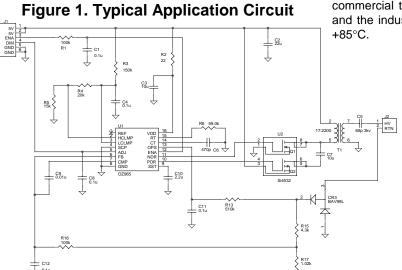

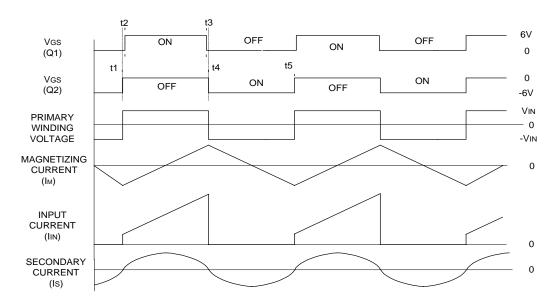

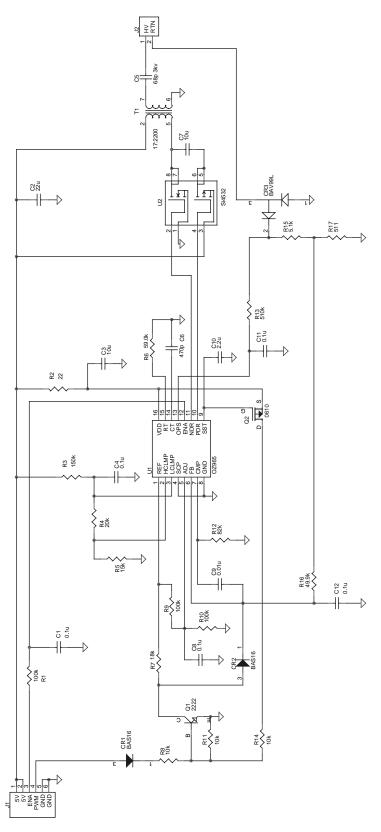

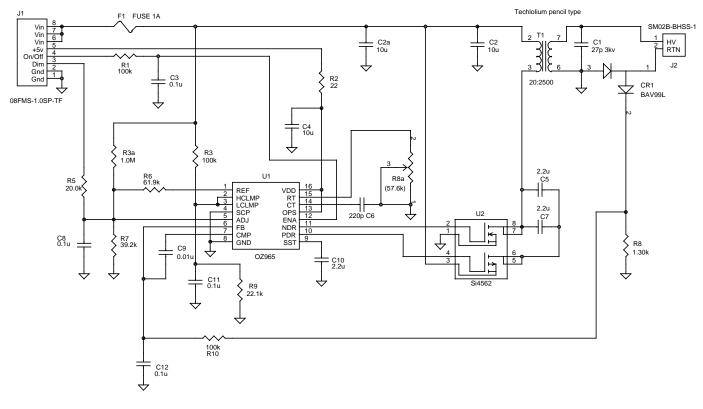

Referring to the schematic shown in Figure 1, the OZ965 operates at a selectable constant frequency through C6 and R6 in pin 14 and Pin 15. It drives one pair of N- and P- power MOSFET switches, Q1 and Q2. These two switches operate in a complementary duty-cycle mode. In other words, Q2 is turned on after Q1 is turned off and vice versa. Figure 2 shows the functional blocks of the OZ965. The OZ965 provides about 250ns of delay for the breakbefore-make circuit to ensure Q1 and Q2 will never be turned on simultaneously. Figure 1 shows a typical application circuit with input voltage of 5V. The power train circuit includes T1, C7, U2, and C5. The transformer T1 is subjected to a rectangular switching waveform. The current and voltage waveform seen at the CCFL load are quasi-sinusoidal.

Using a large capacitance for C7 allows the steady-state voltage across C7 to assume a dc value of  $V_{C7} = -V_{IN} \cdot D/(1-D)$ , where D is the turn-on duty cycle of Q1. Notice that in the OZ965, the minimum duty cycle of Q1 is set at 6%.

In normal operation, Q1's duty cycle is tuned to 0.5 at a full-load condition. Referring to Figure 3 (on page 6), at the beginning of a positive half-cycle,  $\bf t1$ , Q2 turns off. Q1 turns on shortly after at  $\bf t2$ . The magnetizing current,  $\bf l_M$ , increases by a rate of  $\bf V_{IN}/\bf L_M$ , where  $\bf L_M$  is the primary-side magnetizing inductance of the transformer T1. The induced voltage on the secondary winding is positive with respect to the assigned polarity of the transformer. Output current flows from the upper end of the winding through the output capacitor, C5, and into the upper end of the CCFL. While Q1 is on, the transformer transfers

energy to the secondary side through a "forward" coupling effect, similar to a forward dc-dc converter. The waveforms and the corresponding timing of the primary winding voltage, magnetizing current, input current, and secondary current are shown in Figure 3, on page 6.

Q1 turns off at the end of the positive half-cycle, t3. A portion of the magnetizing current is now diverted to flow through C7 and the intrinsic drain-source diode of Q2. As a result, the voltage applied across the primary winding and the secondary winding both become negative. Meanwhile, the magnetizing current flows from the lower end of the secondary winding into the lower end of the CCFL.

The turn-off of Q1 initiates the negative half-cycle. Q2 turns on shortly after at **t4**. The dc voltage on C7 resets the magnetizing current and the transformer core flux. Q2 turns off at the end of the negative half-cycle, **t5**. This forces the primary current to move from Ground through the intrinsic source-drain diode of Q1, the primary winding, and back into the power source. Shortly after Q2 turns off, Q1 turns on again, starting a new positive half-cycle.

Notice that during the positive half-cycle, the input current is the sum of the magnetizing and reflected output currents,  $I_S \bullet N_2/N_1.$  During the negative half-cycle, the magnetizing current essentially supports all the output current. In effect, the transformer transfers energy to the secondary side with the same coupled-inductor characteristics as a "flyback" dc-dc converter.

Figure 3. Typical voltage and current waveforms at 50% duty cycle

### 2. Transformer Design

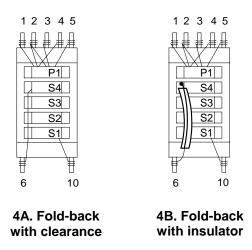

#### 2.1. Transformer in conventional inverter

To support high-voltage ac for driving a CCFL, the transformer's secondary winding typically has a few thousand of turns. Normally, these are divided into a few sections (for a sectioned bobbin). To avoid high voltage crossover, between sections, the maximum voltage differential is limited to less than few hundred Volts. The treatment for the finishing wire is a major engineering challenge. Another type of design is to have the secondary winding wound around a ferrite post. The high voltage differential is made possible by a good-quality manufacturing winding layers are where the properly manipulated.

In the case of sectioned-bobbin transformer, as shown in Figure 4A, the conventional current-fed Royer backlight inverter uses three primary windings sharing the same section P1, occupying 5 pins. The secondary winding is wound over sections S1 to S4. The starting wire of the secondary winding ties to Pin 10. The finishing wire has to cross all secondary-winding sections to finish at Pin 6. Consequently, this fold-back lead wire requires sufficient clearance from the winding surface (see Figure 4A). Alternatively, a layer of Mylar™ or other insulation material may be placed between the fold-back wire and the winding surface of sections S1 to S4, shown in Figure 4B, to avoid high voltage crossover.

The fold-back treatment complicates the transformer manufacturing. In addition, the fold-back structure is prone to arcing failures, particularly with narrow-body transformers.

Figure 4. Conventional Transformer structure

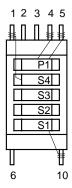

## 2.2. The OZ965 Inverter's transformer structure

The transformer for the OZ965 inverter is much simpler than those in conventional current-fed Royer inverters. There is only one primary winding and one secondary winding, requiring only four pins for termination. Further, the pin-out structure of the bobbin is very flexible. For instance, the primary winding can be wound first and tied to Pin 4 and Pin 5. The secondary is then wound with the starting wire tied to Pin 10, and the finishing wire tied to Pin 1, without applying an insulation tape layer. See Figure 5.

This simplified bobbin structure and the removal of the fold-back design greatly improve the transformer's reliability and lower manufacturing cost. Further, the overall transformer size is reduced to a minimum with the bobbin and pins' simplification.

Figure 5. Two-winding structures without fold-back

### 3. Stray Capacitance and Quasi-Resonance

A backlight system's stray capacitance partially consists of the inter-winding capacitance from the transformer's secondary winding. Additional stray capacitance from the high-voltage wiring, tube,

LCD frame, and foil reflector also adds to the overall amount.

Even a small stray capacitance as little as 10 pF can generate a significant amount of leakage current. To minimize stray capacitance, it is advantageous to integrate the stray capacitance as part of the wave-shaping element.

In general, the high isolation-voltage requirement mandates that primary and secondary windings be wound on separate sections on the bobbin. Consequently, the coupling between the two windings tends to be loose, and leakage inductances high.

When properly utilized, the resonant effect between the transformer's leakage inductance and the stray capacitance can provide sinusoidal voltage and current waveforms even if the transformer is driven by square-wave voltage. By applying this quasi-resonant effect, the OZ965 inverter achieves balanced, sinusoidal drive waveforms while utilizing a constant-frequency, PWM control.

### 4. Operating Frequency

In general, most CCFLs can operate over a wide frequency range. For notebook computer applications, the recommended operating frequency ranges between 30 KHz and 100 KHz. Operating at a lower frequency will create audible noise and require larger inductive and capacitive components. Operating above 100 KHz, on the other hand, will generate excessive stray capacitance losses. For small LCD panels, operating the inverter at higher frequencies seem to have less impact on the losses.

For OZ965 inverter designs, setting the switching frequency slightly higher than the secondary resonant frequency will result in sinusoidal waveforms over a wide range of lamp current. An efficient design should take into consideration all stray capacitance and leakage inductance.

Notice that for the OZ965, the typical oscillator frequency is determined by the following equation as a reference:

Fosc=1.91/(RT•CT)

RT is the resistor connected from Pin 15 to ground and CT is the capacitor connected from Pin 14 to ground.

### 5. Reset Capacitor

The magnetizing inductance of the transformer,  $L_M$ , and the reset capacitor, C6, reset each other in a natural manner. Refer to Figure 1. The absolute voltage on C7,  $V_{C7}$  is determined by the following equation to satisfy the balanced-flux of the transformer for each switching cycle

$$V_{C7} = V_{IN} \cdot D / (1-D)$$

D is the duty cycle of Q1. This capacitor is larger enough to ensure a dc voltage across it.

#### 6. Power MOSFET Selection

The OZ965 is designed to drive high power MOSFETs. For example, the total gate charge of 25nC for both N- and P- MOSFETs can be easily driven through the OZ965. It provides a good solution for high-power applications.

# 7. Regulation and Dimming Control

In Fig. 1, the current sense resistor, R17, detects the lamp current for each half period. This rectified lamp current is integrated through an error amplifier, which consists of Pins 5, 6 and 7 of the OZ965. Notice that this average voltage at Pin 6 relates to the RMS lamp current through a conversion factor of VFB=(0.45•R17)•I(Lmp). Vary the reference voltage at ADJ, one achieves the dimming control to the CCFL. This reference pin accepts an integrated PWM signal or an analog control signal or another form — potentiometer.

Lately, digital dimming and contrast control using hot keys (Fn keys) are also gaining popularity. Digital controls are more reliable than mechanical potentiometer devices. (For digital dimming control capabilities, please refer to the OZ968, OZ969 SMBus Smart Inverter Controller devices.)

### 8. Soft-Start Timing

To avoid over-shoot and inrush current problems, a soft start-up function is provided. The driving pulse width increases gradually after the inverter is powered on. The lamp current starts once the striking voltage reached. This lamp current increases as the driving pulse width increases until the regulated current is achieved. The driving pulse follows the error amplifier's command. In the time that the error amplifier's output reaches the SST potential, the soft-start

current is reduced to 2.5uA, which increases the ignition time needed for regular LCD panels.

#### 9. Enable

The "Enable" signal applied to the ENA(Pin 12) initiates the starting of the inverter. Internal in IC provides a hysteresis comparator to the ENA signal so as to avoid any bi-stable mode of operation. It is always good practice to filter out any undesired noise at this pin. Notice that during shut-down condition (when ENA pin is low), both Q1 and Q2 are off. The soft-start function is always active every time when the enable signal is asserted "high".

# 10. Over-Voltage Protection and Short-Circuit Protection

R13 and C11 serve as noise filter for the detected lamp current. When the signal at OPS is greater than 0.6 Volt, it commands the controller to allow a maximum duty cycle determined by the HCLMP potential. On the other hand, if this signal is lower than 0.6 Volt, the LCLMP determines the maximum duty cycle. This provides a highdegree of flexibility to select transformers. High voltage transformers, unlike a well-couple design, possess a high leakage inductance and experience resonance. This resonance. depending upon the quality-factor of the equivalent circuit, generates a very high voltage that may damage the insulation. This can be seen from a practical open-lamp test. The OZ965 provides a user-programmable open-lamp protection circuit. This is to address the different characteristics of the transformers used in the inverters. For each transformer, applying with different operating frequency and different driving pulse width, its output response differs significantly. One is able to determine the optimum driving condition for the transformer and the LCD panels by selecting proper driving duty cycle, which could be determined by the potential at "HCLMP" and "LCLMP" pins. The formula for

calculating the maximum duty cycle with respect to the set points is:

Dmax= 0.95-0.45Vset; Vset<1.8V

where Vset is the potential at "HCLMP" or "LCLMP". One can adjust these two set points according to the characteristics of the transformer and the loads. In an open-lamp condition, the driving pulse duty cycle is designed to provide sufficient output voltage yet safely operate the transformer. Once the striking period times out under open-lamp condition, the output drive will be terminated and the controller is in a shut-down and latch condition.

In an output short-circuit condition, the input current ramps up rapidly with a high RMS value. The SCP pin (Pin 4) detects an abnormal high potential and executes a shut-down and latch routine. It requires the restart of VDD to resume normal operation.

During the start-up stage, both the open-lamp and short-circuit protections are inhibited. In many designs, up to 1 second of soft-start time is required to guarantee sufficient output voltage to ignite the CCFL at low temperatures.

Note: A couple of application circuits and their tested data are shown at the end of this document (pages 13 – 19).

## **APPLICATION INFORMATION**

1. Typical Application Circuit with PWM Burst-Mode Control

## **PACKAGE INFORMATION**

## **APPLICATION CIRCUITS AND TESTED DATA**

## Reference 1. Application Schematic: PWM Burst-mode dimming control

### **Test Report**

## I: Lamp Current vs. Line Voltage:

| PWM Duty Cycle(%) | Vin(V) | Iin(A) | Pin(w) | Ilamp(ma) |

|-------------------|--------|--------|--------|-----------|

| 100               | 13.0   | 0.34   | 4.39   | 5.35      |

| 100               | 11.0   | 0.40   | 4.40   | 5.32      |

| 100               | 9.5    | 0.47   | 4.44   | 5.29      |

## **II: Lamp Current vs. PWM Duty Cycle:**

| PWM Duty Cycle (%) | Vin(V) | Iin(A) | Pin(w) | Ilamp(ma) |

|--------------------|--------|--------|--------|-----------|

| 100                | 11.0   | 0.40   | 4.40   | 5.32      |

| 90                 | 11.0   | 0.36   | 3.96   | 4.94      |

| 80                 | 11.0   | 0.30   | 3.30   | 4.49      |

| 70                 | 11.0   | 0.25   | 2.75   | 3.98      |

| 60                 | 11.0   | 0.20   | 2.20   | 3.46      |

| 50                 | 11.0   | 0.15   | 1.65   | 2.92      |

| 40                 | 11.0   | 0.10   | 1.10   | 2.34      |

| 30                 | 11.0   | 0.06   | 0.66   | 1.69      |

| 25                 | 11.0   | 0.04   | 0.44   | 1.24      |

| 20                 | 11.0   | 0.01   | 0.11   | 0.00      |

## **III: Efficiency Measurements with Resistor Load:**

| PWM Duty Cycle (%) | Vin(V) | Iin(A) | Pin(w) | Iload(ma) | Load(kohm) | Efficiency |

|--------------------|--------|--------|--------|-----------|------------|------------|

| 100                | 13.0   | 0.420  | 5.460  | 5.58      | 151        | 0.86       |

| 100                | 11.0   | 0.490  | 5.390  | 5.53      | 151        | 0.86       |

| 100                | 9.5    | 0.568  | 5.396  | 5.53      | 151        | 0.86       |

## IV: Open-lamp protection test: Passed.

## V: High temperature over-stress test

| Ambient Temperature ** | Vin(V) | Iin(A) | Pin(w)* | Time     |

|------------------------|--------|--------|---------|----------|

| 25 Degree C            | 13.0   | 0.37   | 4.81    | 1 hour   |

| 40 Degree C            | 13.0   | 0.37   | 4.81    | 1 hour   |

| 50 Degree C            | 13.0   | 0.37   | 4.81    | 1 hour   |

| 60 Degree C            | 13.0   | 0.37   | 4.81    | 1 hour   |

| 70 Degree C            | 13.0   | 0.37   | 4.81    | 1 hour   |

| 80 Degree C            | 13.0   | 0.37   | 4.81    | 1 hour   |

| 90 Degree C            | 13.0   | 0.37   | 4.81    | 1 hour   |

| 100 Degree C           | 13.0   | 0.37   | 4.81    | 12 hours |

| 110 Degree C           | 13.0   | 0.37   | 4.81    | 2 hours  |

<sup>\*</sup> Tested with resistor load of 151k ohms

### VI: Test condition and equipment used

Ambient temperature: 25 deg. C

Scope: Tektronix TDS 360, S/N: B017232

Current probe: Tektronix P6022, S/N: 011-0160-00 High voltage probe: Tektronix P6015A, S/N: B038261

Panel: Samsung 14.1" LCD panel, model LT141x5.124, S/N: 3N8G01517F

Multimeter: HP34401A, S/N: US36037402

Power supply: Tektronix PS2521S, S/N: TW50808

Temperature chamber: Lunaired Limited, model: TJR, S/N: 26214-17

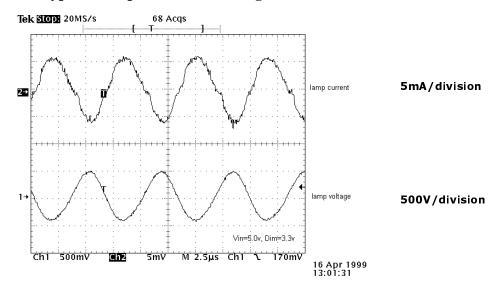

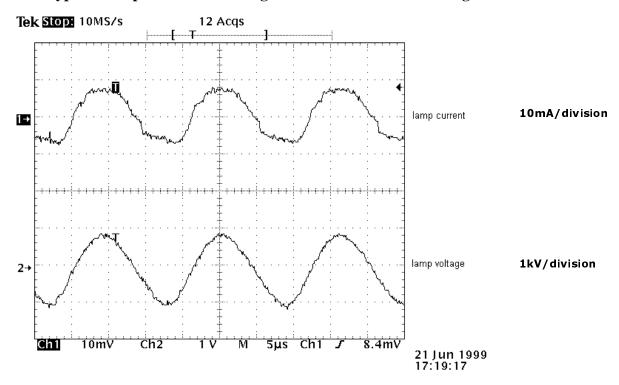

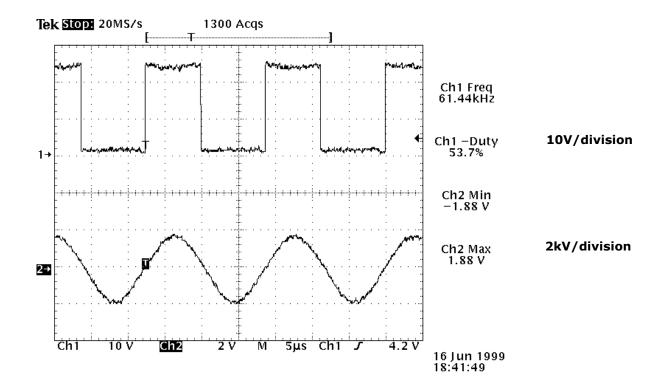

## VII: Typical Lamp Current & Voltage Waveforms 100% Dimming:

## VIII: Typical striking voltage Waveforms:

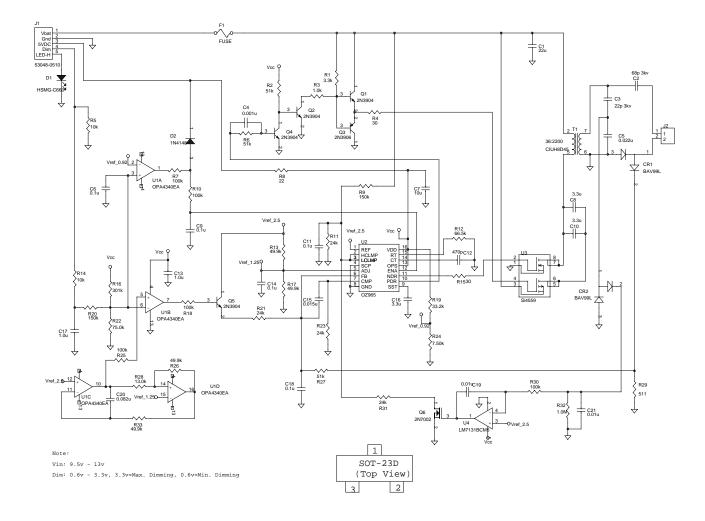

## Reference 2. Application Schematic: Analog dimming control

Vin: Input voltage, 3.0v - 5.3v On/Off: On/Off control; 3.3v=on, 0v=off Dim; 0.2-3.3v; 0.2v=1.0ma, 3.3v=4.0ma.

### **Test Report**

### **I: Lamp Current Measurements @ Maximum light Output:**

| Vdim(v) | Vin(V) | Iin(A) | Pin(w) | Ilamp(ma) |

|---------|--------|--------|--------|-----------|

| 3.3     | 5.3    | 0.283  | 1.500  | 3.99      |

| 3.3     | 5.0    | 0.299  | 1.495  | 3.97      |

| 3.3     | 4.5    | 0.330  | 1.485  | 3.94      |

| 3.3     | 4.0    | 0.368  | 1.472  | 3.90      |

| 3.3     | 3.5    | 0.419  | 1.467  | 3.86      |

| 3.3     | 3.0    | 0.493  | 1.479  | 3.83      |

### I: Lamp Current Measurements @ Minimum light Output:

| Vdim(v) | Vin(V) | Iin(A) | Pin(w) | Ilamp(ma) |

|---------|--------|--------|--------|-----------|

| 0.2     | 5.3    | 0.096  | 0.509  | 0.96      |

| 0.2     | 5.0    | 0.102  | 0.510  | 0.95      |

| 0.2     | 4.5    | 0.112  | 0.504  | 0.94      |

| 0.2     | 4.0    | 0.123  | 0.492  | 0.93      |

| 0.2     | 3.5    | 0.139  | 0.487  | 0.92      |

| 0.2     | 3.0    | 0.161  | 0.483  | 0.91      |

### **II: Efficiency Measurements with Resistor Load:**

| Vdim(v) | Vin(v) | Iin(A) | Pin(w) | Iload(ma) | Load(kohm) | Efficiency(%) |

|---------|--------|--------|--------|-----------|------------|---------------|

| 3.4     | 5.3    | 0.281  | 1.489  | 4.02      | 76         | 82.5          |

| 3.4     | 5.0    | 0.294  | 1.470  | 4.01      | 76         | 83.1          |

| 3.4     | 4.5    | 0.323  | 1.454  | 3.98      | 76         | 82.8          |

| 3.4     | 4.0    | 0.356  | 1.424  | 3.95      | 76         | 83.3          |

| 3.4     | 3.5    | 0.401  | 1.404  | 3.92      | 76         | 83.2          |

| 3.4     | 3.0    | 0.463  | 1.389  | 3.89      | 76         | 82.8          |

### III: Test condition and equipment used

Ambient temperature: 25 deg. C

Scope: Tektronix TDS 360, S/N: B017232

Current probe: Tektronix P6022, S/N: 011-0160-00 High voltage probe: Tektronic P6015A, S/N: B038261 Panel type: SharpLQ0DAs0141, S/N: 9200005 Multimeter: HP34401A, S/N: US36037402

Power supply: Tektronix PS2521S, S/N: TW50808

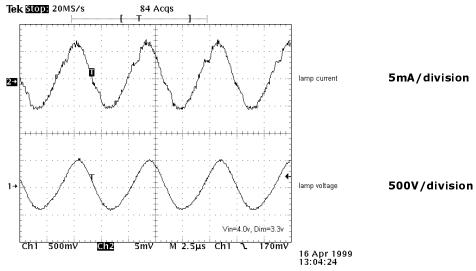

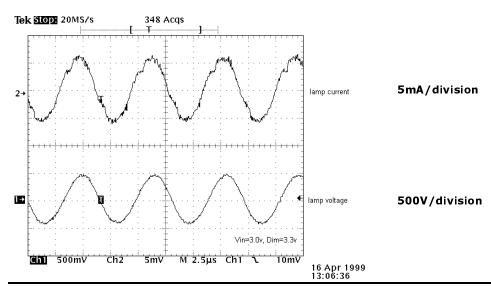

## **IV: Typical Lamp Current & Voltage Waveforms:**