# HIGH-SPEED ARITHMETIC LOGIC

S54181 N74181

S54181-N,F,Q • N74181-N,F

#### DESCRIPTION

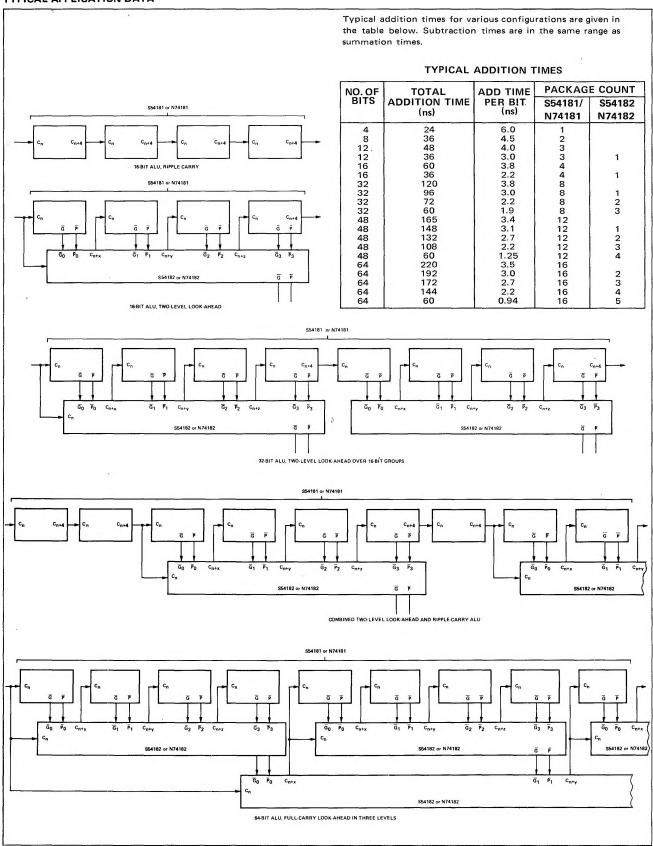

The 54181 and 74181 are high-speed arithmetic logic units (ALU)/ function generators which have a complexity of 75 equivalent gates on a monolithic chip. This circuit performs 16 binary arithmetic operations on two 4-bit words as shown in the function table. These operations are selected by the four function-select lines (S0, S1, S2, S3) and include addition, subtraction, decrement, and straight transfer. When performing arithmetic manipulations, the internal carries must be enabled by applying a low-level voltage to the mode control input (M). A full carry look-ahead scheme is made available in the 54181/74181 for fast, simultaneous carry generation with a group carry propagate (P) and carry generate (G) for the 4 bits in the package. When used in conjunction with the 54182 or 74182 full carry look-ahead circuits, high-speed arithmetic operations can be performed. For example, the typical addition time for the 54181/74181 is 24 nanoseconds for 4 bits. When expanding to 16-bit addition with the 54182/74182, only 13 nanoseconds, further delay is added so that the total addition time is 35 nanoseconds, or 2.2 nanoseconds per bit. One 54182/74182 is needed for every 16 bits (four 54181/74181 circuits).

These circuits have been designed to not only incorporate all of the designer's requirements for arithmetic operations, but also to provide 16 possible functions of two Boolean variables without the use of external circuitry. These logic functions are selected by use of the four function-select inputs (SO, S1, S2, S3) with the mode control input (M) at a high level to disable the internal carry. The 16 logic functions are detailed in the function table and include exclusive-OR, NAND, AND, NOR and OR functions.

The 54181/74181 is designed with a Darlington output configuration (54H/74H type) to reduce the high-logic-level output impedance and thereby improve the turn-off propagation delay time. All outputs are rated at a normalized fan-out of ten at the low logic level and increased to a fan-out of 20 at the high logic level. The increased high-logic-level fan-out allows the system designer more freedom in tying unused inputs to driven inputs.

## DIGITAL 54/74 TTL SERIES

The 54181 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C; the 74181 is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

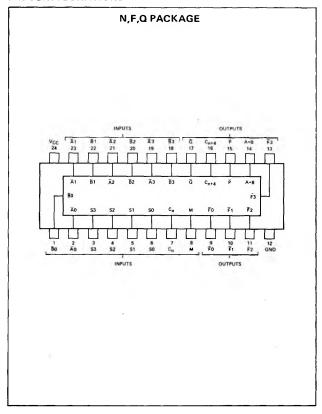

#### **PIN CONFIGURATIONS**

#### TRUTH TABLES

#### **TABLE OF ARITHMETIC OPERATIONS**

| FUNCTION<br>SELECT |    |      |    | OUTPUT FUNCTION                 |                           |  |  |  |

|--------------------|----|------|----|---------------------------------|---------------------------|--|--|--|

| S3                 | S2 | S1 . | S0 | LOW LEVELS<br>ACTIVE            | HIGH LEVELS<br>ACTIVE     |  |  |  |

| L                  | L  | L    | L  | F = A minus 1                   | F = A                     |  |  |  |

| L                  | L  | L    | Н  | F = AB minus 1                  | F = A+B                   |  |  |  |

| L                  | L  | Н    | L  | F = AB minus 1                  | F = A+B                   |  |  |  |

| L                  | L  | H    | Н  | F = minus 1 (2's                | F = minus 1 (2's          |  |  |  |

|                    |    |      |    | complement)                     | complement)               |  |  |  |

| L                  | Н  | L    | L  | $F = A plus (A + \overline{B})$ | F = A plus AB             |  |  |  |

| L                  | н  | L    | Н  | $F = AB plus (A+\overline{B})$  | F = (A+B) plus AB         |  |  |  |

| L                  | Н  | Н    | L  | F=A minus B minus 1             | F=A minus B minus         |  |  |  |

| L                  | Н  | Н    | Н  | F = A+B                         | F = AB minus 1            |  |  |  |

| Н                  | L  | L    | L  | F = A plus (A+B)                | F = A plus AB             |  |  |  |

| Н                  | L  | L    | Н  | F = A plus B                    | F = A plus B              |  |  |  |

| Н                  | L  | Н    | L  | F=AB plus (A+B)                 | F=(A+B) plus AB           |  |  |  |

| Н                  | L  | Н    | Н  | F = A+B                         | F = AB minus 1            |  |  |  |

| Н                  | Н  | L    | L  | F = A plus A <sup>†</sup>       | F = A plus A <sup>†</sup> |  |  |  |

| Н                  | Н  | L    | н  | F = AB plus A                   | F=(A+B) plus A            |  |  |  |

| Н                  | Н  | Н    | L  | F = AB plus A                   | F=(A+B) plus A            |  |  |  |

| Η,                 | Н  | Н    | н  | F = A                           | F = A minus 1             |  |  |  |

#### TABLE OF LOGIC FUNCTIONS

| FUNCTION<br>SELECT |            |   |    | OUTPUT FUNCTION |                     |  |  |  |

|--------------------|------------|---|----|-----------------|---------------------|--|--|--|

| S3                 | 3 S2 S1 S0 |   | S0 | NEGATIVE LOGIC  | POSITIVE LOGIC      |  |  |  |

| Ŀ                  | L          | L | L  | F = Ā           | F = Ā               |  |  |  |

| L                  | L          | L | н  | F = AB          | F = A+B             |  |  |  |

| L                  | L          | н | L  | F = A+B         | F = AB              |  |  |  |

| L                  | L          | Н | н  | F=Logical 1     | F=Logical 0         |  |  |  |

| L                  | н          | L | L  | F = A+B         | $F = \overline{AB}$ |  |  |  |

| L                  | н          | L | н  | F = B           | F = B               |  |  |  |

| L                  | Н          | н | L  | F=A + B         | F=A + B             |  |  |  |

| L                  | Н          | н | Н  | F = A+B         | F = AB              |  |  |  |

| н                  | L          | L | L  | F = AB          | F = A+B             |  |  |  |

| Н                  | L          | L | Н  | F=A + B         | F=A + B             |  |  |  |

| Н                  | L          | н | L  | F = B           | F = B               |  |  |  |

| Н                  | L          | н | Н  | F = A+B         | F = AB              |  |  |  |

| Н                  | Н          | Ł | L  | F= Logical 0    | F=Logical 1         |  |  |  |

| Н                  | Н          | L | н  | F = AB          | F = A+B             |  |  |  |

| н                  | Н          | Н | L  | F = AB          | F = A+B             |  |  |  |

| Н                  | н          | Н | н  | F = A           | F = A               |  |  |  |

# SIGNETICS DIGITAL 54/74 TTL SERIES S54181 ● N74181

NOTES:

With mode control (M) and  $\mathbf{C}_{\mathbf{n}}$  low  $^{\dagger}$  Each bit is shifted to the next more significant position.

With mode control (M) high:  $\mathbf{C}_{\mathbf{n}}$  irrelevant For positive logic: logical 1 = high voltage

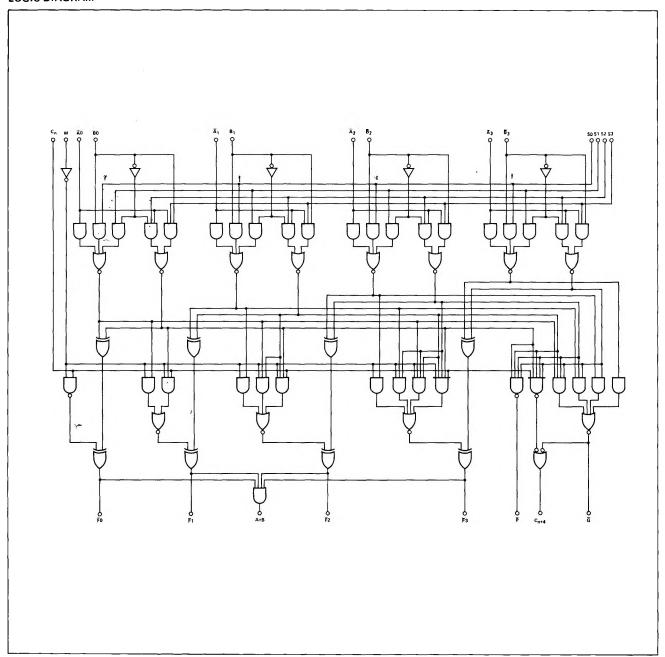

## LOGIC DIAGRAM

## RECOMMENDED OPERATING CHARACTERISTICS

|                                                          | \$54181 |     |     |      |     |      |      |

|----------------------------------------------------------|---------|-----|-----|------|-----|------|------|

|                                                          | MIN     | NOM | MAX | MIN  | NOM | MAX  | UNIT |

| Supply Voltage V <sub>CC</sub>                           | 4.5     | 5   | 5.5 | 4.75 | 5   | 5.25 | V    |

| Normalized Fan-Out from each Output, N: High logic level |         |     | 20  |      |     | 20   |      |

| Low logic level                                          |         |     | 10  |      |     | 10   |      |

| Operating Free-Air Temperature Range, TA                 | -55     | 25  | 125 | 0    | 25  | 70   | °c   |

ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER        |                                             | TEST CONDITIONS*                                  |                                                   |        | MIN | TYP** | MAX  | UNIT |

|------------------|---------------------------------------------|---------------------------------------------------|---------------------------------------------------|--------|-----|-------|------|------|

| VIH              | High-level input voltage                    |                                                   |                                                   |        | 2   |       |      | v    |

| VIL              | Low-level input voltage                     |                                                   |                                                   |        |     |       | 8.0  | V    |

| v <sub>OH</sub>  | High-level output voltage                   | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8V, | V <sub>IH</sub> = 2V,<br>I <sub>OH</sub> = -800μA |        | 2.4 |       |      | V    |

| VOL              | Low-level output voltage                    | $V_{CC} = MIN,$<br>$V_{IL} = 0.8V,$               |                                                   |        |     |       | 0.4  | V    |

| ЧН               | High-level input current (mode input)       |                                                   |                                                   |        | 1   |       | 40   | μΑ   |

| <sup>1</sup> IH  | High-level input current (any A or B input) | V - MAY                                           | V - 2 4V                                          |        |     |       | 120  | μА   |

| Чн               | High-level input current (any S input)      | V <sub>CC</sub> = MAX,                            | V <sub>1</sub> = 2.4V                             |        |     |       | 160  | μΑ   |

| Iн               | High-level input current (carry input)      |                                                   |                                                   |        |     |       | 200  | μА   |

| I <sub>IH</sub>  | High-level input current (any input)        | V <sub>CC</sub> = MAX,                            | V <sub>I</sub> = 5.5V                             |        | 1   |       | 1    | mA   |

| IIL              | Low-level input current (mode input)        |                                                   |                                                   |        |     |       | -1.6 | mA   |

| 1 <sub>1</sub> L | Low-level input current (any A or B input)  | V <sub>CC</sub> = MAX,                            | $V_1 = 0.4V$                                      |        |     |       | -4.8 | mA   |

| I <sub>I</sub> L | Low-level input current (any S input)       | VCC - WAA,                                        | V1 - 0.4V                                         |        | ļ   |       | -6.4 | mA   |

| I <sub>IL</sub>  | Low-level input current (carry input)       |                                                   |                                                   |        |     |       | -8   | mA   |

|                  | Short-circuit output current                | \ - MAY                                           |                                                   | S54181 | -20 |       | -55  |      |

| los              | Short-circuit output current                | V <sub>CC</sub> = MAX                             |                                                   | N74181 | -18 |       | -57  | mA   |

| 1                | Supply current                              |                                                   |                                                   | S54181 |     | 88    | 127  |      |

| 1CC              | Supply culterit                             | V <sub>CC</sub> = MAX                             |                                                   | N74181 |     | 88    | 140  | mA   |

| ,                | Supply gurrant                              | 1,, ,,,,,                                         |                                                   | S54181 |     | 94    | 135  |      |

| 1cc              | Supply current                              | V <sub>CC</sub> = MAX                             |                                                   | N74181 | ļ   | 94    | 150  | mA.  |

# SWITCHING CHARACTERISTICS, V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C, N = 10 (C<sub>L</sub> = 15pF, R<sub>L</sub> = 400 $\Omega$ )

| PARAMETER¶        | FROM (INPUT)   | TO (OUTPUT)                   | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|-------------------|----------------|-------------------------------|----------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH  | c <sub>n</sub> | c <sub>n+4</sub>              |                            |     | 12  | 18  | ns   |

| <sup>t</sup> PHL  | " "            | 1174                          |                            |     | 13  | 19  |      |

| t <sub>PLH</sub>  | c <sub>n</sub> | Any F                         | M = 0V                     |     | 13  | 19  | ns   |

| <sup>t</sup> PHL  | _ \            | A A                           | (SUM or DIFF mode)         |     | 12  | 18  |      |

| t <sub>PLH</sub>  | Any A or B     | $\overline{G}$                | M = 0V, $S0 = S3 = 4.5V$ , |     | 13  | 19  |      |

| t <sub>PHL</sub>  | Ally A or B    | G                             | S1 = S2 = 0V (SUM mode)    |     | 13  | 19  | ns   |

| t <sub>P</sub> LH | Any A or B     | $\overline{G}$                | M = 0V, S0 = S3 = 0V,      |     | 17  | 25  |      |

| t <sub>PHL</sub>  | Ally A of B    | G                             | S1 = S2 = 4.5V (DIFF mode) |     | 17  | 25  | ns   |

| t <sub>PLH</sub>  | Any Ā or B     | P                             | M = 0V, $S0 = S3 = 4.5V$ , |     | 13  | 19  |      |

| t <sub>PHL</sub>  | Any A or B     | r                             | S1 = S2 = 0V (SUM mode)    |     | 17  | 25  | ns   |

| t <sub>PLH</sub>  | Any A or B     | Ē                             | M = 0V, S0 = S3 = 0V,      |     | 17  | 25  |      |

| t <sub>PHL</sub>  | Any A or B     | P                             | S1 = S2 = 4.5V (DIFF mode) |     | 17  | 25  | ns   |

| t <sub>PLH</sub>  |                | 4                             | M = 0V, S0 = S3 = 4.5V,    |     | 28  | 42  |      |

| t <sub>PHL</sub>  | Any A or B     | Any F                         | S1 = S2 = 0V (SUM mode)    |     | 21  | 32  | ns   |

| t <sub>PLH</sub>  |                |                               | M = 0V, S0 = S3 = 0V,      |     | 32  | 48  |      |

| t <sub>PHL</sub>  | Any A or B     | Any F                         | S1 = S2 = 4.5V (DIFF mode) |     | 23  | 34  | ns   |

| t <sub>PLH</sub>  |                |                               | M = 4.5V (logic model)     |     |     |     |      |

| t <sub>PHL</sub>  | Any A or B     | Any F                         | W - 4.5V (rogic moder)     |     | 32  | 48  | ns   |

| t <sub>PLH</sub>  | 3/0            |                               | M = 0V CO = C2 = 0V        |     | 23  | 34  |      |

| t <sub>PHL</sub>  | Any A or B     | $\overline{A} = \overline{B}$ | M = 0V, S0 = S3 = 0V,      |     | 35  | 50  | ns   |

| , AHC             |                |                               | S1 = S2 = 4.5V (DIFF mode) |     | 32  | 48  | 115  |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable

<sup>\*\*</sup> All typical values are at  $V_{CC} = 5V$ ,  $T_{A} = 25^{\circ}C$ .

$<sup>\</sup>Pt_{PLH}$  = propagation delay time, low-to-high-level output  $t_{PHL}$  = propagation delay time, high-to-low-level output

#### TYPICAL APPLICATION DATA