# PurePath Digital™ AUDIO SIX-CHANNEL PWM PROCESSOR

#### **FEATURES**

- Audio Input/Output

- Automatic Master Clock Rate and Data Sample Rate Detection

- Four Serial Audio Inputs (Eight Channels)

- Support for 32-, 44.1-, 48-, 88.2-, 96-, 176.4-, and 192-kHz Sampling Rates

- Data Formats: 16-, 20-, or 24-Bit Input Data;

Left-Justified, Right-Justified, and I<sup>2</sup>S

- 64- or 48-f<sub>S</sub> Bit-Clock Rate

- 128-, 192-, 256-, 384-, and 512-f<sub>S</sub> Master

Clock Rates (Up to a Maximum of 50 MHz)

- Six PWM Audio Output Channels

- Any Output Channel Can be Mapped to Any Output Pin

- Supports Single-Ended and Bridge-Tied Loads

- I<sup>2</sup>S Serial Audio Output

- Audio Processing

- Volume Control Range of 48 dB to -100 dB

- Master Volume Control from 24 dB to -100 dB in 0.5-dB Increments

- Six Individual Channel Volume Controls With 24-dB to -100-dB Attenuation in 0.5-dB Increments

- Serial Output Can Be Produced by Downmix of 5.1-Channel Input or Fourth Serial Input

- 5.1-Channel Downmix to 2.1 or 3.1 PWM

Output Speaker System

- Integrated Bass Management

- Two Programmable Biquads in Subwoofer Channel

- Full Six-Channel Input and Output Mapping

- Selectable DC Blocking Filters

- PWM Processing

- 8x Oversampling With Fourth-Order Noise Shaping at 44.1, 48 kHz; 4x Oversampling at 88.2, 96 kHz; 2x Oversampling at 176.4, 192 kHz; and 12x Oversampling at 32 kHz

- ≥105-dB Dynamic Range (TAS5086+TAS5186)

- THD < 0.06% (TAS5086 Only)</li>

- 20-Hz-20-kHz Flat Noise Floor for 44.1-, 48-, 88.2-, 96-, 176.4- and 192-kHz Data Rates

- Digital De-Emphasis for 32-kHz, 44.1-kHz and 48-kHz Data Rates

- Intelligent AM Interference Avoidance System Provides Clear AM Reception

- Optimized PWM Sequence for Click- and Popless Start and Stop

- Optimized PWM Sequence for Charging of AC-Coupling Capacitors in Single-Ended Configurations

- Adjustable Modulation Limit From 93.8% to 99.2%

- General Features

- Automated Operation With Easy-to-Use Control Interface

- I<sup>2</sup>C Serial Control Slave Interface

- Control Interface Operational Without MCLK

- Single 3.3-V Power Supply

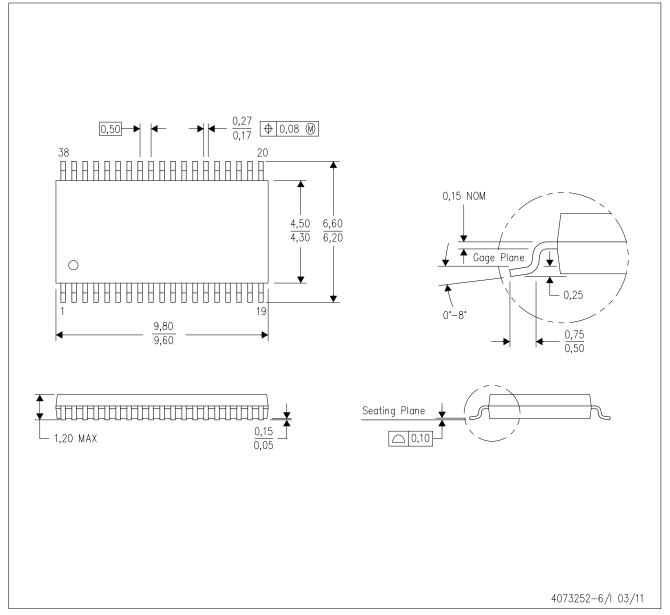

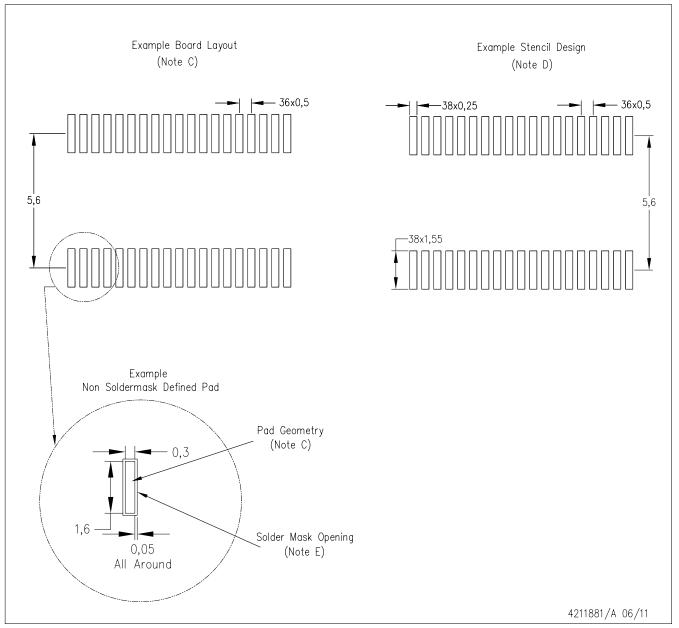

- 38-Pin TSSOP Package

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PurePath Digital is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### DESCRIPTION

The TAS5086 is a six-channel digital pulse-width modulator (PWM) that provides both advanced performance and a high level of system integration. The TAS5086 is designed to interface seamlessly with most audio digital signal processors and MPEG decoders, accepting a wide range of input data and clock formats.

The TAS5086 drives six channels of speakers in either single-ended or bridge-tied load configurations that accept a 1N + 1 interface format. The TAS5086 also supports 2N + 1 power stages with the use of some external logic (e.g., TAS5112). Stereo line out in I<sup>2</sup>S format is available with either a pass-through signal (SDIN4) or an internal downmix.

The TAS5086 uses AD modulation operating at a 384-kHz switching rate for 32-, 44.1-, 48-, 88.2-, 96-, 176.4-, and 192-kHz data. The 8x oversampling, combined with the 4th-order noise shaper, provides a broad, flat noise floor and excellent dynamic range from 20 Hz to 20 kHz.

The TAS5086 is only an  $I^2C$  slave device, which always receives MCLK, SCLK, and LRCLK from other system components. The TAS5086 accepts clock rates of 128, 192, 256, 384, and 512  $f_S$ . The TAS5086 accepts a 64- $f_S$  master clock for 176.4-kHz and 192-kHz data.

The TAS5086 accepts a 64- $f_S$  bit clock for all data rates. The TAS5086 also can accept a 48- $f_S$  SCLK rate for MCLK ratios of 192  $f_S$  and 384  $f_S$ .

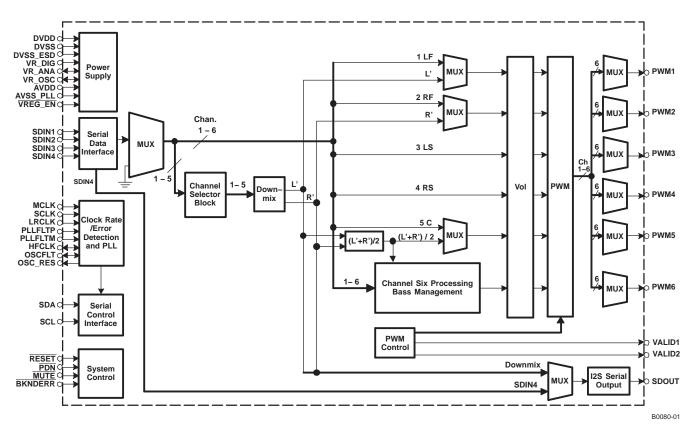

The TAS5086 is composed of five functional blocks.

- Power supply

- · Clock, PLL, and serial data interface

- Serial control interface

- Device control

- PWM section

For detailed application information, see the *Using the PurePath Digital PWM Processor* application report (SLEA046).

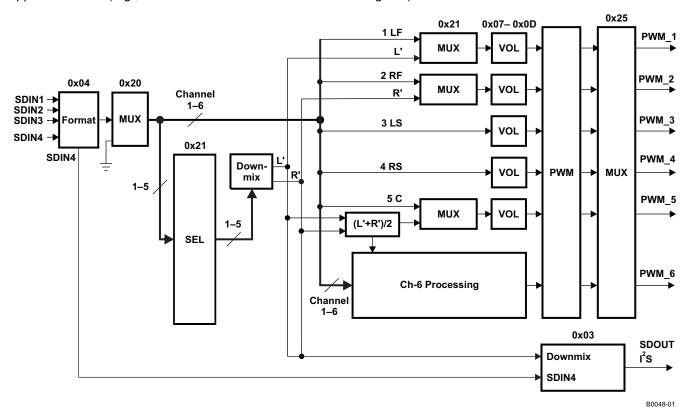

Figure 1 shows the functional structure of the TAS5086.

Figure 1. TAS5086 Functional Block Diagram

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

| Supply voltage     | DVDD and DVD_ESD                                                    | -0.3 V to 3.6 V        |  |

|--------------------|---------------------------------------------------------------------|------------------------|--|

| Supply voltage     | AVDD                                                                | –0.3 V to 3.6 V        |  |

| lanut voltage      | 3.3-V-digital input                                                 | –0.5 V to DVDD + 0.5 V |  |

| Input voltage      | 5-V-tolerant <sup>(2)</sup> digital input                           | –0.5 V to 6 V          |  |

| Input clamp currer | $t,  V_1  < 0 \text{ or } V_1 > 1.8 \text{ V}$                      | ±20 mA                 |  |

| Output clamp curre | ent, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > 1.8 V) | ±20 mA                 |  |

| Operating free-air | temperature                                                         | 0°C to 70°C            |  |

| Storage temperatu  | Storage temperature range, T <sub>stq</sub>                         |                        |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operation conditions" are not implied. Exposure to absolute-maximum conditions for extended periods may affect device reliability.

#### **DISSIPATION RATINGS**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| DBT     | 817.16 mW             | 10.214 mW/C                 | 357.5 mW              | 204.29 mW             |

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                 |                              |                         | MIN | NOM | MAX | UNIT |

|-----------------|------------------------------|-------------------------|-----|-----|-----|------|

|                 | Digital supply voltage       | DVDD                    | 3   | 3.3 | 3.6 | V    |

|                 | Analog supply voltage        | AVDD                    | 3   | 3.3 | 3.6 | V    |

| V <sub>IH</sub> | High-level input voltage     | 3.3-V TTL, 5-V tolerant | 2   |     |     | V    |

| V <sub>IL</sub> | Low-level input voltage      | 3.3-V TTL, 5-V tolerant |     |     | 0.8 | V    |

| T <sub>A</sub>  | Operating ambient-air temper | rature range            | 0   | 25  | 70  | °C   |

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                 | PARAME                               | TER                                       | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |  |

|-----------------|--------------------------------------|-------------------------------------------|------------------------------------|-----|-----|-----|------|--|

| $V_{OH}$        | High-level output voltage            | 3.3-V TTL and 5-V <sup>(1)</sup> tolerant | $I_{OH} = -4 \text{ mA}$           | 2.4 |     |     | V    |  |

| $V_{OL}$        | Low-level output voltage             | 3.3-V TTL and 5-V <sup>(1)</sup> tolerant | I <sub>OL</sub> = 4 mA             |     |     | 0.5 | V    |  |

| l <sub>OZ</sub> | High-impedance output current        | 3.3-V TTL                                 |                                    |     |     | 20  | μΑ   |  |

|                 | Low lovel input ourrent              | 3.3-V TTL                                 | $V_I = V_{IL}$                     |     |     | 1   |      |  |

| I <sub>IL</sub> | Low-level input current              | 5-V tolerant <sup>(2)</sup>               | V <sub>I</sub> = 0 V, DVDD = 3 V   |     |     | 1   | μΑ   |  |

|                 | Lligh lovel input current            | 3.3-V TTL                                 | $V_I = V_{IH}$                     |     |     | 1   |      |  |

| I <sub>IH</sub> | High-level input current             | 5-V tolerant <sup>(2)</sup>               | V <sub>I</sub> = 5.5 V, DVDD = 3 V |     |     | 20  | μΑ   |  |

|                 |                                      |                                           | f <sub>S</sub> = 48 kHz            |     | 140 |     |      |  |

|                 |                                      | Digital average values of DVDD            | f <sub>S</sub> = 96 kHz            |     | 150 |     | A    |  |

|                 | lament annuals, annuals              | Digital supply voltage, DVDD              | f <sub>S</sub> = 192 kHz           |     | 155 |     | mA   |  |

| I <sub>DD</sub> | I <sub>DD</sub> Input supply current |                                           | Power down                         |     | 8   |     |      |  |

|                 |                                      | Analog gunnhu voltage AV/DD               | Normal                             |     | 20  |     | A    |  |

|                 |                                      | Analog supply voltage, AVDD               | Power down                         |     | 2   |     | mA   |  |

<sup>(1) 5-</sup>V-tolerant outputs are SCL and SDA

Product Folder Link(s): TAS5086

<sup>(2) 5-</sup>V tolerant inputs are RESET, PDN, MUTE, SCLK, LRCLK, MCLK, SDA, and SCL.

<sup>(2) 5-</sup>V-tolerant inputs are SDA, SCL, RESET, PDN, MUTE, HP\_SEL, SCLK, LRCLK, MCLK, SDIN1, SDIN2, SDIN3, and SDIN4.

## **Serial Audio Port**

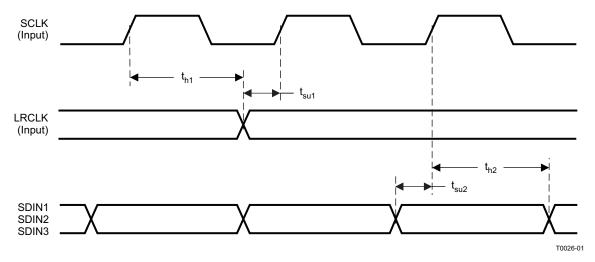

Serial audio port slave mode over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                 | TEST CONDITIONS                                      | MIN   | TYP | MAX    | UNIT           |

|---------------------|-----------------------------------------------------------|------------------------------------------------------|-------|-----|--------|----------------|

| f <sub>SCLKIN</sub> | SCLK input frequency                                      | $C_L = 30 \text{ pF}, \text{ SCLK} = 64 \text{ f}_S$ | 2.048 |     | 12.288 | MHz            |

| t <sub>su1</sub>    | Setup time, LRCLK to SCLK rising edge                     |                                                      | 10    |     |        | ns             |

| t <sub>h1</sub>     | Hold time, LRCLK from SCLK rising edge                    |                                                      | 10    |     |        | ns             |

| t <sub>su2</sub>    | Setup time, SDIN to SCLK rising edge                      |                                                      | 10    |     |        | ns             |

| t <sub>h2</sub>     | Hold time, SDIN from SCLK rising edge                     |                                                      | 10    |     |        | ns             |

|                     | LRCLK frequency                                           |                                                      | 32    | 48  | 192    | kHz            |

|                     | SCLK duty cycle                                           |                                                      | 40%   | 50% | 60%    |                |

|                     | LRCLK duty cycle                                          |                                                      | 40%   | 50% | 60%    |                |

|                     | SCLK rising edges between LRCLK rising edges              |                                                      | 64    |     | 64     | SCLK<br>edges  |

|                     | LRCLK clock edge with respect to the falling edge of SCLK |                                                      | -1/4  |     | 1/4    | SCLK<br>period |

Figure 2. Slave Mode Serial Data Interface Timing

# TAS5086 Pin-Related Characteristics of the SDA and SCL I/O Stages for F/S-Mode I<sup>2</sup>C-Bus Devices

|                  | PARAMETER                                               | TEST CONDITIONS                      | STANDAR             | D MODE       | FAST M                        | ODE               | UNIT |

|------------------|---------------------------------------------------------|--------------------------------------|---------------------|--------------|-------------------------------|-------------------|------|

|                  | FARAWEIER                                               | TEST CONDITIONS                      | MIN                 | MAX          | MIN                           | MAX               | UNII |

| $V_{IL}$         | LOW-level input voltage                                 |                                      | -0.5                | $0.3~V_{DD}$ | -0.5                          | $0.3~V_{DD}$      | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                                |                                      | 0.7 V <sub>DD</sub> |              | 0.7 V <sub>DD</sub>           |                   | V    |

| $V_{hys}$        | Hysteresis of Schmitt-trigger inputs                    |                                      | N/A                 | N/A          | $0.05~\mathrm{V}_\mathrm{DD}$ |                   | V    |

| V <sub>OL1</sub> | LOW-level output voltage (open drain or open collector) | 3-mA sink current                    |                     |              | 0                             | 0.4               | V    |

| t <sub>of</sub>  | Output fall time from $V_{IHmin}$ to $_{VILmax}$        | Bus capacitance from 10 pF to 400 pF |                     | 250          | 7 + 0.1 C <sub>b</sub>        | 250               | ns   |

| t <sub>SP</sub>  | Pulse duration of spikes suppressed (2)                 |                                      | N/A                 | N/A          | 0                             | 30                | ns   |

| li               | Input current, each I/O pin                             |                                      | -30                 | 30           | -30 <sup>(3)</sup>            | 30 <sup>(3)</sup> | μΑ   |

| C <sub>i</sub>   | Capacitance, each I/O pin                               |                                      |                     | 10           |                               | 10                | pF   |

<sup>(1)</sup>  $C_b = \text{capacitance of one bus line in pF}$ . The output fall time is faster than the standard  $I^2C$  specification.

Copyright © 2005–2008, Texas Instruments Incorporated

<sup>(2)</sup> SCL and SDA have a 30-ns glitch filter.

<sup>(3)</sup> The I/O pins of fast-mode devices must not obstruct the SDA and SDL lines if V<sub>DD</sub> is switched off.

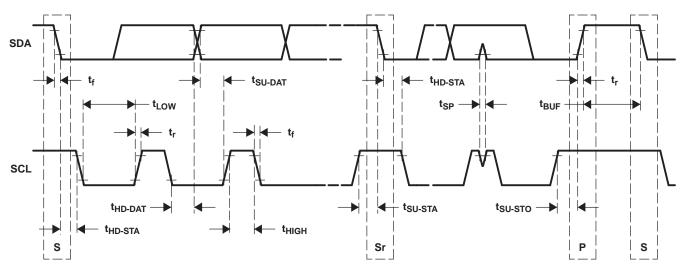

# TAS5086 Bus-Related Characteristics of the SDA and SCL I/O Stages for F/S-Mode I<sup>2</sup>C-Bus Devices

All values are referred to  $V_{IHmin}$  and  $V_{ILmax}$  (see *TAS5086 Pin-Related Characteristics of the SDA and SCL I/O Stages for F/S-Mode I2C-Bus Devices*).

| DADAMETED           |                                                                                                    | TEGT COMPLTIONS | STANDAR             | D MODE  | FAST MO                               | DE                 | LINIT |

|---------------------|----------------------------------------------------------------------------------------------------|-----------------|---------------------|---------|---------------------------------------|--------------------|-------|

|                     | PARAMETER                                                                                          | TEST CONDITIONS | MIN                 | MIN MAX |                                       | MAX                | UNIT  |

| f <sub>SCL</sub>    | SCL clock frequency                                                                                |                 | 0                   | 100     | 0                                     | 400                | kHz   |

| t <sub>HD-STA</sub> | Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. |                 | 4                   |         | 0.6                                   |                    | μs    |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                        |                 | 4.7                 |         | 1.3                                   |                    | μs    |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                       |                 | 4                   |         | 0.6                                   |                    | μs    |

| t <sub>SU-STA</sub> | Setup time for repeated START                                                                      |                 | 4.7                 |         | 0.6                                   |                    | μs    |

| t <sub>SU-DAT</sub> | Data setup time                                                                                    |                 | 250                 |         | 100                                   |                    | μs    |

| t <sub>HD-DAT</sub> | Data hold time (1)(2)                                                                              |                 | 0                   | 3.45    | 0                                     | 0.9                | μs    |

| t <sub>r</sub>      | Rise time of both SDA and SCL                                                                      |                 |                     | 1000    | 7 + 0.1 C <sub>b</sub> <sup>(3)</sup> | 500 <sup>(4)</sup> | ns    |

| t <sub>f</sub>      | Fall time of both SDA and SCL                                                                      |                 |                     | 300     | 7 + 0.1 C <sub>b</sub> <sup>(3)</sup> | 300                | ns    |

| t <sub>SU-STO</sub> | Setup time for STOP condition                                                                      |                 | 4                   |         | 0.6                                   |                    | μs    |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                                   |                 | 4.7                 |         | 1.3                                   |                    | μs    |

| C <sub>b</sub>      | Capacitive loads for each bus line                                                                 |                 |                     | 400     |                                       | 400                | pF    |

| $V_{nL}$            | Noise margin at the LOW level for each connected device (including hysteresis)                     |                 | 0.1 V <sub>DD</sub> |         | 0.1 V <sub>DD</sub>                   |                    | V     |

| $V_{nH}$            | Noise margin at the HIGH level for each connected device (including hysteresis)                    |                 | 0.2 V <sub>DD</sub> |         | 0.2 V <sub>DD</sub>                   |                    | V     |

- (1) Note that SDA does not have the standard I<sup>2</sup>C specification 300-ns hold time and that SDA must be valid by the rising and falling edges of SCL. TI recommends that a 3.3-kΩ pullup resistor be used to avoid potential timing issues.

- (2) A fast-mode I²C-bus device can be used in a standard-mode I²C-bus system, but the requirement t<sub>SU-DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>r-max</sub> + t<sub>SU-DAT</sub> = 1000 + 250 = 1250 ns (according to the standard-mode I²C bus specification) before the SCL line is released.

- (3)  $C_b = total$  capacitance of one bus line in pF.

- (4) Rise time varies with pullup resistor.

Figure 3. Start and Stop Conditions Timing Waveforms

T0114-01

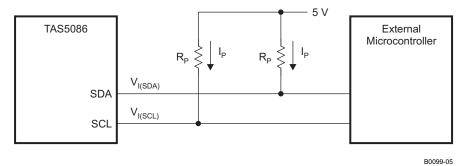

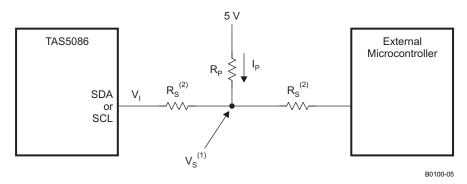

## Recommended I<sup>2</sup>C Pullup Resistors

It is recommended that the I²C pullup resistors  $R_P$  be 3.3 k $\Omega$  (see Figure 4). If a series resistor is in the circuit (see Figure 5), then the series resistor  $R_S$  should be less than or equal to 300  $\Omega$ .

Figure 4. I<sup>2</sup>C Pullup Circuit (With No Series Resistor)

- (1)  $V_S = 5 \times R_S/(R_S + R_P)$ . When driven low,  $V_S << V_{IL}$  requirements.

- (2)  $R_S \le 300 \Omega$

Figure 5. I<sup>2</sup>C Pullup Circuit (With Series Resistor)

Copyright © 2005–2008, Texas Instruments Incorporated

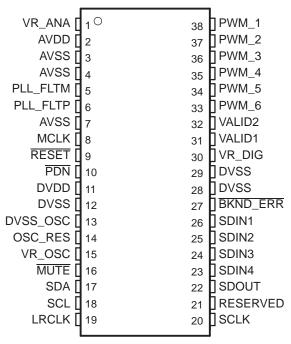

## PHYSICAL CHARACTERISTICS

#### DBT PACKAGE (TOP VIEW)

P0034-01

**Table 1. TERMINAL FUNCTIONS**

| TERMINA  | <b>\L</b>        | I/O <sup>(1)</sup> | 5-V      | TERMINATION <sup>(2)</sup> | DESCRIPTION                                                                                                                                                                                                                           |

|----------|------------------|--------------------|----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.              | 1/0(1)             | TOLERANT | TERMINATION (-)            | DESCRIPTION                                                                                                                                                                                                                           |

| AVDD     | 2                | Р                  |          |                            | 3.3-V analog power supply                                                                                                                                                                                                             |

| AVSS     | 3, 4,<br>7       | Р                  |          |                            | Analog supply ground                                                                                                                                                                                                                  |

| BKND_ERR | 27               | DI                 |          | Pullup                     | Active-low. A back-end error sequence is generated by applying logic LOW to this terminal. BKND_ERR results in no change to any system parameters while VALID2 goes low.                                                              |

| DVDD     | 11               | Р                  |          |                            | 3.3-V digital power supply                                                                                                                                                                                                            |

| DVSS     | 12,<br>28,<br>29 | Р                  |          |                            | Digital ground                                                                                                                                                                                                                        |

| DVSS_OSC | 13               | Р                  |          |                            | Digital ground for oscillator                                                                                                                                                                                                         |

| LRCLK    | 19               | DI                 | 5-V      | Pulldown                   | Input serial audio data left/right clock (sampling rate clock)                                                                                                                                                                        |

| MCLK     | 8                | DI                 | 5-V      | Pulldown                   | MCLK is a 3.3-V clock master clock input. The input frequency of this clock can range from 4 MHz to 50 MHz.                                                                                                                           |

| MUTE     | 16               | DI                 | 5-V      | Pullup                     | Performs a soft mute of outputs, active-low (muted signal = a logic low, normal operation = a logic high). The mute control provides a noiseless volume ramp to silence. Releasing mute provides a noiseless ramp to previous volume. |

| OSC_RES  | 14               | AO                 |          |                            | Oscillator trim resistor                                                                                                                                                                                                              |

<sup>(1)</sup> TYPE: A = analog; D = 3.3-V digital; P = power/ground/decoupling; I = input; O = output

<sup>(2)</sup> All pullups are 20-μA weak pullups, and all pulldowns are 20-μA weak pulldowns. The pullups and pulldowns are included to ensure proper input logic levels if the terminals are left unconnected (pullups => logic 1 input; pulldowns => logic 0 input). Devices that drive inputs with pullups must be able to sink 20 μA while maintaining a logic-0 drive level. Devices that drive inputs with pulldowns must be able to source 20 μA while maintaining a logic-1 drive level.

## Table 1. TERMINAL FUNCTIONS (continued)

| Table 1. TERMINAL FUNCTIONS (continued) |     |                    |                 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------------|-----|--------------------|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TERMINA<br>NAME                         | NO. | I/O <sup>(1)</sup> | 5-V<br>TOLERANT | TERMINATION <sup>(2)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PDN                                     | 10  | DI                 | 5-V             | Pullup                     | Power down, active-low. PDN powers down all logic, stops all clocks, and performs a soft stop whenever a logic low is applied. The internal parameters are preserved through a power-down cycle, as long as RESET is not active. The duration for system recovery from power down is 100 ms. When released, PDN powers up all logic, starts all clocks, and performs a soft start that returns to the previous configuration. |  |  |

| PLL_FLTM                                | 5   | AO                 |                 |                            | PLL negative input                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| PLL_FLTP                                | 6   | Al                 |                 |                            | PLL positive input                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| PWM_ 1                                  | 38  | DO                 |                 |                            | PWM 1 output                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PWM_ 2                                  | 37  | DO                 |                 |                            | PWM 2 output                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PWM_3                                   | 36  | DO                 |                 |                            | PWM 3 output                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PWM_4                                   | 35  | DO                 |                 |                            | PWM 4 output                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PWM_5                                   | 34  | DO                 |                 |                            | PWM 5 output                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PWM_6                                   | 33  | DO                 |                 |                            | PWM 6 output                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RESERVED                                | 21  | -                  |                 |                            | RESERVED (connect to ground)                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RESET                                   | 9   | DI                 | 5-V             | Pullup                     | A system reset is generated by applying a logic low to this terminal. RESET is an asynchronous control signal that restores the TAS5086 to its default conditions, sets the VALID2 output low, and places the PWM in the hard-mute (M) state. Master volume is immediately set to full attenuation. On the release of RESET, if PDN is high, the system performs a 4–5-ms device initialization and sets the volume at mute.  |  |  |

| SCL                                     | 18  | DI                 | 5-V             |                            | I <sup>2</sup> C serial control clock input                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SCLK                                    | 20  | DI                 | 5-V             | Pulldown                   | Serial audio data clock (shift clock). SCLKIN is the serial audio port (SAP) input data bit clock.                                                                                                                                                                                                                                                                                                                            |  |  |

| SDA                                     | 17  | DIO                | 5-V             |                            | I <sup>2</sup> C serial control data interface input/output                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SDIN1                                   | 26  | DI                 |                 | Pulldown                   | Serial audio data 1 input is one of the serial data input ports. SDIN1 supports four discrete (stereo) data formats.                                                                                                                                                                                                                                                                                                          |  |  |

| SDIN2                                   | 25  | DI                 |                 | Pulldown                   | Serial audio data 2 input is one of the serial data input ports. SDIN2 supports four discrete (stereo) data formats.                                                                                                                                                                                                                                                                                                          |  |  |

| SDIN3                                   | 24  | DI                 |                 | Pulldown                   | Serial audio data 3 input is one of the serial data input ports. SDIN3 supports four discrete (stereo) data formats.                                                                                                                                                                                                                                                                                                          |  |  |

| SDIN4                                   | 23  | DI                 |                 | Pulldown                   | Serial audio data 4 input is one of the serial data input ports. SDIN4 supports four discrete (stereo) data formats.                                                                                                                                                                                                                                                                                                          |  |  |

| SDOUT                                   | 22  | DI                 |                 |                            | Serial audio data 1 output is the only serial data output port. SDOUT supports I <sup>2</sup> S format only.                                                                                                                                                                                                                                                                                                                  |  |  |

| VALID1                                  | 31  | DO                 |                 |                            | Soft start valid. Output indicating validity of soft-start PWM output, active-high                                                                                                                                                                                                                                                                                                                                            |  |  |

| VALID2                                  | 32  | DO                 |                 |                            | Output indicating validity of PWM outputs, active-high.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| VR_ANA                                  | 1   | Р                  |                 |                            | Voltage reference for analog supply, 1.8 V. A pinout of the internally regulated 1.8-V power. A 0.1- $\mu$ F, low-ESR capacitor should be connected between this terminal and AVSS_PLL. This terminal must not be used to power external devices.                                                                                                                                                                             |  |  |

| VR_DIG                                  | 30  | Р                  |                 |                            | Voltage reference for digital PWM core supply, 1.8 V. A pinout of the internally regulated 1.8-V power used by digital PWM core logic. A 0.1-µF, low-ESR <sup>(3)</sup> capacitor should be connected between this terminal and DVSS_PWM. This terminal must not be used to power external devices.                                                                                                                           |  |  |

| VR_OSC                                  | 15  | Р                  |                 |                            | Voltage reference for analog supply, 1.8 V. A pinout of the internally regulated 1.8-V power. A 0.1-μF, low-ESR <sup>(3)</sup> capacitor should be connected between this terminal and AVSS_PLL. This terminal must not be used to power external devices.                                                                                                                                                                    |  |  |

<sup>(3)</sup> If desired, low-ESR capacitance values can be implemented by paralleling two or more ceramic capacitors of equal value. Paralleling capacitors of equal value provides an extended high-frequency supply decoupling. This approach avoids the potential of producing parallel resonance circuits that have been observed when paralleling capacitors of different values.

Copyright © 2005–2008, Texas Instruments Incorporated

#### **DETAILED DESCRIPTION**

#### **POWER SUPPLY**

The TAS5086 power-supply section contains regulators that provide analog and digital regulated power for various sections of the TAS5086. The analog supply supports the analog PLL while digital supplies support the digital PLL, the digital audio processor, the pulse width modulator, and the output control (reclocker). The power-supply section is enabled via VREG\_EN.

## **CLOCK, ERROR RATE DETECTION, AND PLL**

This module provides the timing and serial data interface for the TAS5086.

The TAS5086 is a clock slave device. It accepts MCLK, SCLK, and LRCLK.

The TAS5086 supports 64-f<sub>s</sub> MCLK for the 176.4-kHz and 192-kHz data rates.

The TAS5086 accepts a 64-f $_{\rm S}$  SCLK rate for all MCLK ratios and a 48-f $_{\rm S}$  SCLK rate for MCLK ratios of 192 f $_{\rm S}$  and 384 f $_{\rm S}$ .

TAS5086 checks to verify that SCLK is a specific value of 64 f<sub>S</sub> or 48 f<sub>S</sub>.

The TAS5086 supports a 1-f<sub>S</sub> LRCLK.

The timing relationship of these clocks to SDIN[1:4] and SDOUT is shown in subsequent sections.

The clock section uses MCLK or the internal oscillator clock (when MCLK is unstable or absent) to produce a 196-MHz PLL output.

The TAS5086 can auto-detect and set the internal clock control logic to the appropriate settings for the frequencies of 32 kHz, normal speed (44.1 or 48 kHz), double speed (88.2 kHz or 96 kHz), and quad speed (176.4 kHz or 192 kHz). The automatic sample rate detection can be disabled and the values set via I<sup>2</sup>C.

The TAS5086 also supports an AM interference-avoidance mode during which the clock rate is adjusted, in concert with the PWM sample rate converter, to produce a PWM output at 7-f<sub>S</sub>, 8-f<sub>S</sub>, or 9-f<sub>S</sub>.

The sample rate must be set manually during AM interference avoidance and when de-emphasis is enabled.

The TAS5086 uses an internal oscillator time base to provide reference timing information for the following functions:

- MCLK, SCLK, and LRCLK error detection

- I<sup>2</sup>C communication when power is first applied to the device

- Automatic data-rate detection and setting (32 kHz, normal, double, and quad speed)

- Automatic MCLK rate detection and setting (64, 128, 192, 256, 384, and 512 f<sub>s</sub>)

#### **OSCILLATOR TRIM**

The TAS5086 PWM processor contains an internal oscillator for PLL reference. This reduces system cost because an external reference is not required. After each power up or reset, a oscillator trim is needed; see the Oscillator Trim Register (0x1B) section for a detailed procedure.

#### **SERIAL DATA INTERFACE**

Serial data is input on SDIN1, SDIN2, SDIN3, and SDIN4. The PWM outputs and downmix are derived from SDIN1, SDIN2, and SDIN3. SDIN4 is a selectable pass-through signal that is available at SDOUT as an  $I^2S$  output. The TAS5086 accepts 32-, 44.1-, 48-, 88.2-, 96-, 176.4-, and 192-kHz serial data in 16-, 20-, or 24-bit, left-justified, right-justified, and  $I^2S$  serial data formats.

Serial data is output on SDOUT. The SDOUT data format is  $I^2S$  24-bit at the same data rate as the input. The SDOUT output is synchronized to use the SCLK and LRCLK signals. There is a 1- to 2.5-LRCLK frame delay from the input data to the output data, depending on the input serial data format. The SDOUT output has no  $I^2C$ -controllable functions. It is always operational.

The parameters of this clock and serial data interface input format are I<sup>2</sup>C configurable.

# I<sup>2</sup>C SERIAL CONTROL INTERFACE

The TAS5086 has an I<sup>2</sup>C serial control slave interface to receive commands from a system controller. The serial control interface supports both normal-speed (100-kHz) and high-speed (400-kHz) operations without wait states. As an added feature, this interface operates even if MCLK is absent.

The serial control interface supports both single-byte and multi-byte read and write operations for status registers and the general control registers associated with the PWM.

The I<sup>2</sup>C interface supports a special mode that permits I<sup>2</sup>C write operations to be broken up into multiple-data write operations that are multiples of 4 data bytes. These are 6-, 10-, 14-, 18-, ... etc., -byte write operations that are composed of a device address, read/write bit, subaddress, and any multiple of 4 bytes of data. This permits the system to write large register values incrementally without blocking other I<sup>2</sup>C transactions.

Figure 6 shows the data flow and control through the TAS5086. The major I<sup>2</sup>C registers are shown above each applicable block (e.g., 0x04 is the serial data format control register).

Figure 6. TAS5086 Data Flow Diagram With I<sup>2</sup>C Registers

Copyright © 2005–2008, Texas Instruments Incorporated

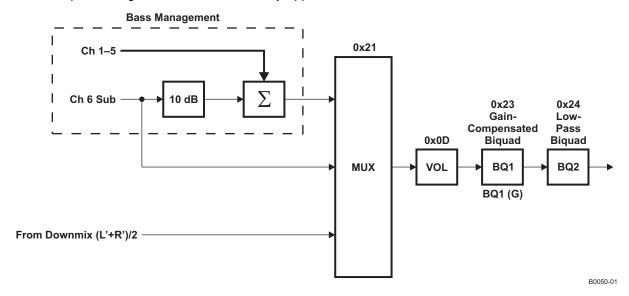

## **Channel-6 Processing Section**

Channel 6 has processing features that are directly applicable to the subwoofer channel.

Figure 7. Channel-6 Processing Block Diagram

#### **PWM Section**

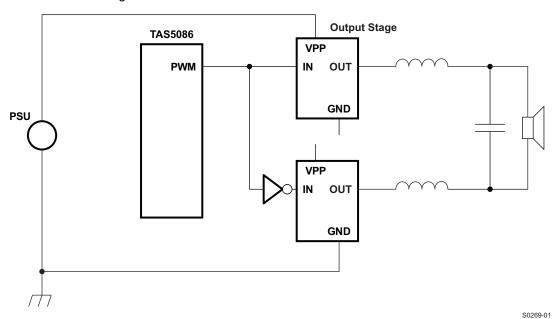

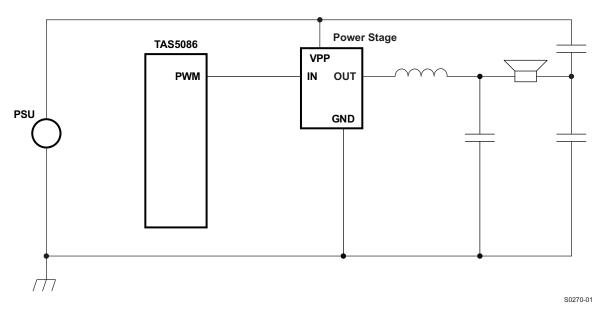

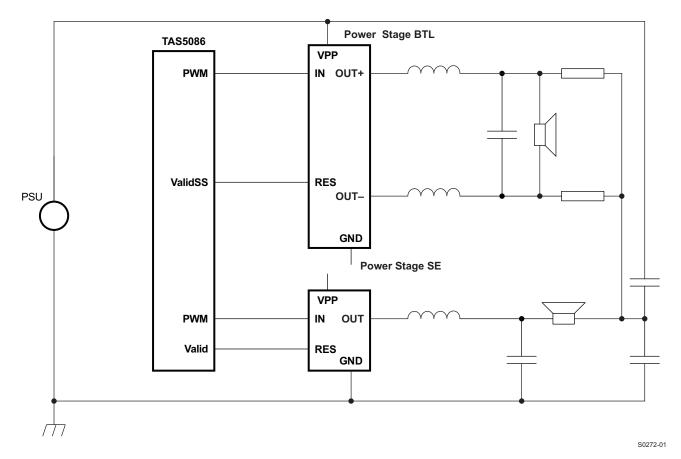

The TAS5086 has six channels of high-performance digital PWM modulators that are designed to drive switching output stages (back ends) in both single-ended (SE) and H-bridge (bridge-tied load) configurations. The TAS5086 device uses noise-shaping and sophisticated error correction algorithms to achieve high power efficiency and high-performance digital audio reproduction. The TAS5086 uses a fourth-order noise shaper to provide >105-dB SNR performance from 20 Hz to 20 kHz.

The TAS5086 PWM interface is described by using the following notation:

PN + V

where

P = number of PWM signals per channel

N = number of channels

V = total number of valid signals used to reset the power stage

For example, the TAS5086 initial interface format means that there is 1 PWM signal per channel (N = 6) and 1 valid signal is used to reset the power stages. The shorthand notation to describe this is 1N+1.

The PWM section accepts 24-bit PCM data from the serial data interface and outputs six PWM audio output channels to drive 1N+1 single-ended and BTL power stages.

The PWM interface supports:

- TAS5186 in BTL or SE mode without any external glue logic, uses 1N+1 signaling.

- TAS5142 in BTL or SE mode without any external glue logic, uses 1N+1 signaling.

- TAS5111 SE without any external glue logic, and with a pulldown on the output, uses 1N+1 signaling.

- TAS5111 BTL or TAS5112 BTL with one inverter per BTL channel of glue logic and a pulldown on the output, uses 1N+1 signaling from TAS5086, 2N+1 input to TAS5111/12.

- TAS5112 SE (with external glue logic)

See the application schematics for an example of the TAS5086 with the TAS5186 and the TAS5086 with TAS5112 SE and TAS5111 SE.

The TAS5086 has input multiplexers that allow any of the input channels to be routed to any PWM channel and output multiplexers to enable any PWM output to be routed to any PWM output pin.

It also has individual channel dc-blocking filters that are enabled by default.

Individual channel de-emphasis filters for 32, 44.1, and 48 kHz are included and can be enabled and disabled.

There is also a two-channel downmix result that can be output on SDOUT (I<sup>2</sup>S format). This result also can be sent to the left and right front channels (channels 1 and 2) and/or to the center and subwoofer (channels 5 and 6) as well.

A mixer on the subwoofer channel supports bass management configuration 1.

#### PWM output characteristics

- Up to 8x oversampling

- 12x at  $f_S = 32$  kHz, 8x at  $f_S = 48$  kHz, 4x at  $f_S = 96$  kHz, 2x at  $f_S = 192$  kHz

- · Fourth-order noise shaping

- ≥105-dB dynamic range, 0–20 kHz (TAS5086 + TAS5186 system measured at speaker terminals)

- THD < 0.06% (measured at TAS5086 outputs)

- Adjustable maximum modulation limit of 93.8% to 99.2%

## **Transitions Between Shutdown and Playing**

The TAS5086 outputs are switching all the time with the noise shaper active. Mute is acheived by inputting a zero into the noise shaper, with the noise shaper running and the output still switching. By using this approach, the transitions between off and operation is avoided. The only exception is shutdown of surround channels as described in the *Surround Register (0x19)* section.

Futhermore, the TAS5086 is designed to drive a load in single-ended and bridge-tied-load configurations. The *principle* in the SE and BTL configurations is shown in Figure 8 and Figure 9. In both situations, care must be taken to ensure correct start-up sequences which charge the bootstrap capacitor and do not produce audible artifacts; the TAS5086 is designed to do that.

Figure 8. BTL Filter Configuration

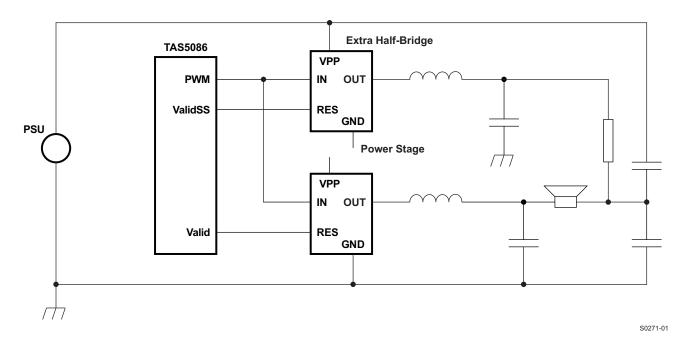

The SE configuration presents an additional challenge in order for starting up quietly. The second terminal of the loudspeaker is connected to a split capacitor between power and ground. The advantage of this circuitly is that it provides some degree of power-supply ripple rejection. The problem related to the split capacitor is that the voltage over it must be controlled when the modulator starts (i.e., when the power stage output goes out of high impedance state) to avoid a click in the speaker.

Copyright © 2005–2008, Texas Instruments Incorporated

Figure 9. SE Filter Configuration

The TAS5086 supports two mechanisms for controlling the split-capacitor midpoint.

In the extra half-bridge scheme (the TAS5186 power stage is an example of this) an additional half-bridge is started and brought to a 50-percent duty cycle, i.e., a situation where the average voltage of the half-bridge is equal to the voltage which must be applied to the split-capacitor midpoint to start up without clicks in the speaker. A resistor per channel is connected between the extra half-bridge and each midpoint for the split capacitors. The split capacitors are charged through this resistor. This approach requires an extra VALID pin on the modulator to control the extra half-bridge, therefore the 1N+2 interface. Figure 10 shows the topology of the extra half-bridge. In some situations, a channel configured in BTL can be used to charge the split capacitor instead of the extra half-bridge. This is shown in Figure 11.

The mid-Z scheme charges the split capacitor through the loudspeaker. In order to do this without audible artifacts the charge current must be limited. This is done by applying a start sequence which charges the output state between low, high and high-Z. Because the ouput stage is in high-Z in a part of the sequence, the resulting output impedance can be brought to a level suitable for charging the split capacitors without audible artifacts. This solution does not require external components, as shown in Figure 9. Not all power stages are compatible with the mid-Z scheme, double-check the power-stage data sheet for compabitility. The PWM start register (0x18) programs the TAS5086 for mid-Z or the standard low-Z start sequence.

Figure 10. Split-Capacitor Charging With Extra Half-Bridge

Figure 11. Split-Capacitor Charging With BTL Subwoofer

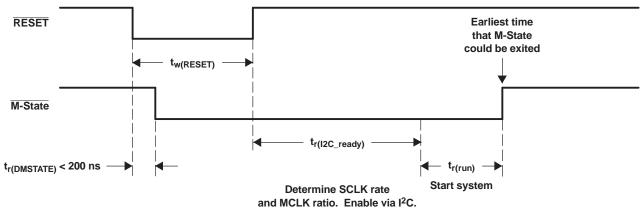

## **Reset Timing (RESET)**

Control-signal parameters over recommended operating conditions (unless otherwise noted)

T0029-03

|                           | PARAMETER                       | MIN | TYP | MAX  | UNIT |

|---------------------------|---------------------------------|-----|-----|------|------|

| t <sub>r(DMSTATE)</sub>   | Time to M-STATE low             |     |     | 370  | ns   |

| t <sub>w(RESET)</sub>     | Pulse duration, RESET active    | 400 |     | None | ns   |

| t <sub>r(I2C_ready)</sub> | Time to enable I <sup>2</sup> C |     | 3   |      | ms   |

| t <sub>r(run)</sub>       | Device start-up time            | 10  |     |      | ms   |

NOTE: Because a crystal time base is used, the system determines the CLK rates. Once the data rate and master clock ratio are determined, the system outputs audio if a master volume command is issued.

Figure 12. Reset Timing

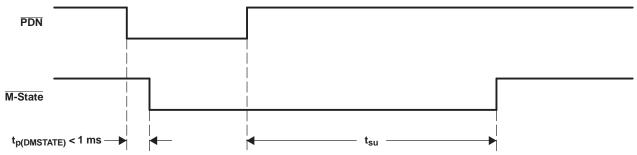

# Power-Down (PDN) Timing

Control-signal parameters over recommended operating conditions (unless otherwise noted). Note that  $\overline{PDN}$  does not clear I<sup>2</sup>C registers.

T0030-02

|                         | PARAMETER                                    | MIN | TYP | MAX | UNIT |

|-------------------------|----------------------------------------------|-----|-----|-----|------|

| t <sub>p(DMSTATE)</sub> | Time to M-STATE low                          |     |     | 300 | μs   |

|                         | Number of MCLKs preceding the release of PDN | 5   |     |     |      |

| t <sub>su</sub>         | Device start-up time                         |     | 120 |     | ms   |

Figure 13. Power-Down Timing

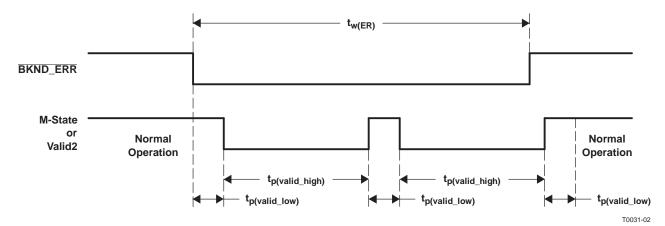

# Back-End Error (BKND\_ERR)

Control-signal parameters over recommended operating conditions (unless otherwise noted)

Control-signal parameters over recommended operating conditions (unless otherwise noted)

|                            | PARAMETER                                              | MIN | TYP MAX | UNIT          |

|----------------------------|--------------------------------------------------------|-----|---------|---------------|

| $t_{w(ER)}$                | Pulse duration, BKND_ERR active                        | 350 | None    | ns            |

| t <sub>p(valid_low)</sub>  |                                                        |     | <100    | μs            |

| t <sub>p(valid_high)</sub> | I <sup>2</sup> C programmable to be between 1 to 10 ms | -25 | 25      | % of interval |

Figure 14. Error Recovery Timing

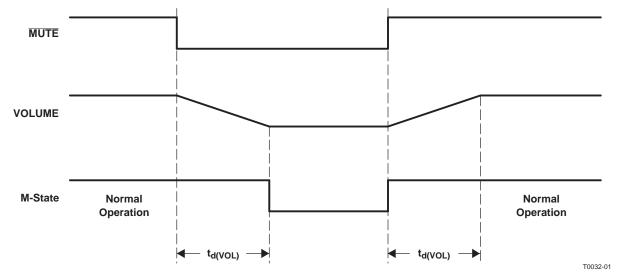

# Mute Timing (MUTE)

Control-signal parameters over recommended operating conditions (unless otherwise noted). Note that MUTE does not stop PWM switching; it stops the noise shaper, and therefore has less noise.

| PARAMETER                            | MIN     | TYP             | MAX               | UNIT |

|--------------------------------------|---------|-----------------|-------------------|------|

| t <sub>d(VOL)</sub> Volume ramp time | Defined | by rate setting | ng <sup>(1)</sup> | ms   |

(1) See the Volume Control Register (0x0E) section.

Figure 15. Mute Timing

#### SERIAL INTERFACE CONTROL AND TIMING

## I2S TIMING

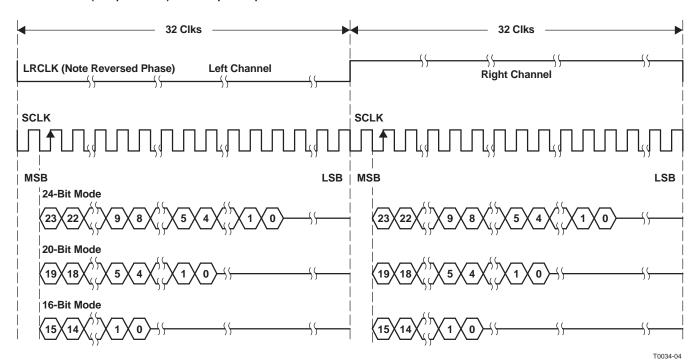

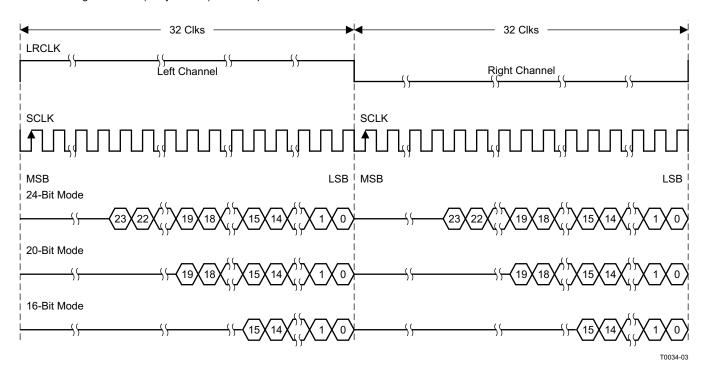

$I^2S$  timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is low for the left channel and high for the right channel. A bit clock running at 64  $f_S$  is used to clock in the data. A delay of one bit clock occurs from the time the LRCLK signal changes state to the first bit of data on the data lines. The data is written MSB-first and is valid on the rising edge of the bit clock. The TAS5086 masks unused trailing data bit positions.

#### 2-Channel I2S (Philips Format) Stereo Input/Output

Figure 16. I<sup>2</sup>S 64-f<sub>S</sub> Format

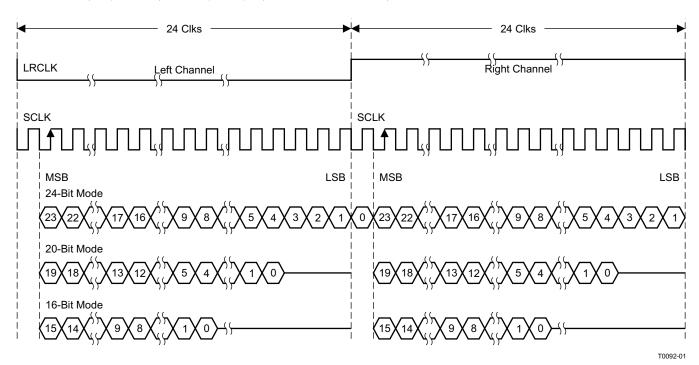

2-Channel I<sup>2</sup>S (Philips Format) Stereo Input/Output (24-Bit Transfer Word Size)

Figure 17. I<sup>2</sup>S 48-f<sub>S</sub> Format

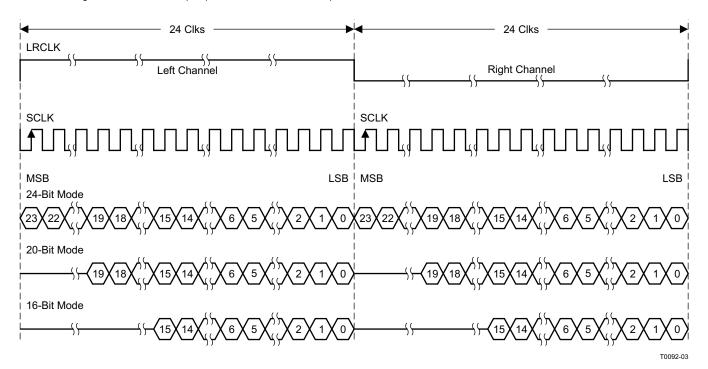

## **LEFT-JUSTIFIED**

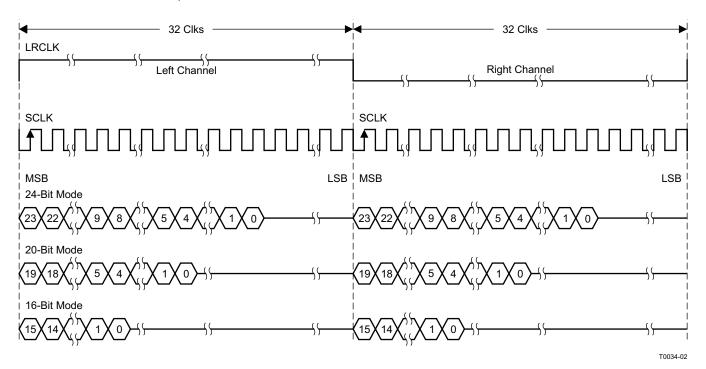

Left-justified (LJ) timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is high for the left channel and low for the right channel. A bit clock running at 64  $f_S$  is used to clock in the data. The first bit of data appears on the data lines at the same time LRCLK toggles. The data is written MSB-first and is valid on the rising edge of the bit clock. The TAS5086 masks unused trailing data bit positions.

Copyright © 2005–2008, Texas Instruments Incorporated

## 2-Channel Left-Justified Stereo Input

Figure 18. Left-Justified 64-f<sub>S</sub> Format

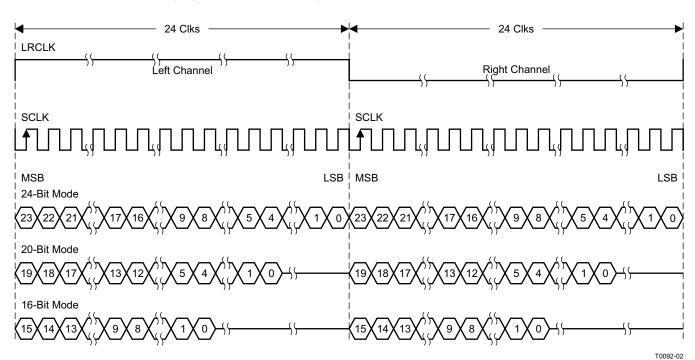

## 2-Channel Left-Justified Stereo Input (24-Bit Transfer Word Size)

Figure 19. Left-Justified 48-f<sub>S</sub> Format

## **Right-Justified**

Right-justified (RJ) timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is high for the left channel and low for the right channel. A bit clock running at 64 f<sub>S</sub> is used to clock in the data. The first bit of data appears on the data 8 bit-clock periods (for 24-bit data) after LRCLK toggles. In RJ mode, the LSB of data always is clocked by the last bit clock before LRCLK transitions. The data is written MSB-first and is valid on the rising edge of bit clock. The TAS5086 masks unused leading data bit positions.

2-Channel Right-Justified (Sony Format) Stereo Input

Figure 20. Right-Justified 64-f<sub>S</sub> Format

2-Channel Right-Justified Stereo Input (24-Bit Transfer Word Size)

Figure 21. Right-Justified 48-f<sub>S</sub> Bit Format

#### I<sup>2</sup>C SERIAL CONTROL INTERFACE

The TAS5086 has a bidirectional Inter IC (I<sup>2</sup>C) interface that is compatible with the I<sup>2</sup>C bus protocol and supports both single- and multiple-byte write and read operations. The control interface is used to program the registers of the device and to read device status.

The TAS5086 supports wait-state insertions by other I<sup>2</sup>C devices on the bus. However, the TAS5086 performs all I<sup>2</sup>C operations without I<sup>2</sup>C wait cycles.

The TAS5086 supports standard-mode I<sup>2</sup>C bus operation (100 kHz maximum) and fast I<sup>2</sup>C bus operation (400 kHz maximum).

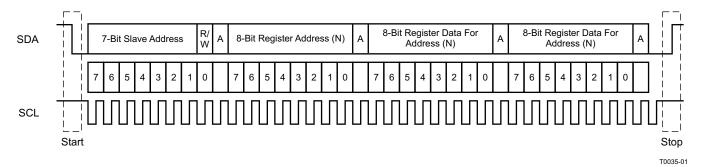

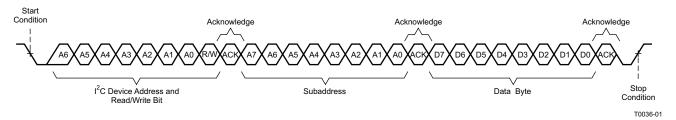

#### GENERAL I<sup>2</sup>C OPERATION

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially, one bit at a time. The address and data are transferred in byte (8-bit) format with the most-significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period. These conditions are shown in Figure 22. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then wait for an acknowledge condition. The TAS5086 holds SDA low during the acknowledge clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pullup resistor must be used for the SDA and SCL signals to set the HIGH level for the bus.

Figure 22. Typical I<sup>2</sup>C Sequence

An unlimited number of bytes can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 22.

The 7-bit address for the TAS5086 is 0011 011.

#### SINGLE- AND MULTIPLE-BYTE TRANSFERS

The serial control interface supports both single-byte and multiple-byte read/write operations for status registers and the general control registers associated with the PWM. However, for the DAP data processing registers, the serial control interface supports only multiple-byte (4-byte) read/write operations.

During multiple-byte read operations, the TAS5086 responds with data, a byte at a time, starting at the subaddress assigned, as long as the master device continues to respond with acknowledges. If a particular subaddress does not contain 32 bits, the unused bits are read as logic 0.

During multiple-byte write operations, the TAS5086 compares the number of bytes transmitted to the number of bytes that are required for each specific subaddress. If a write command is received for a biquad subaddress, the TAS5086 expects to receive five 32-bit words. If fewer than five 32-bit data words have been received when a stop command (or another start command) is received, the data received is discarded. Similarly, if a write command is received for a mixer coefficient, the TAS5086 expects to receive one 32-bit word.

Supplying a subaddress for each subaddress transaction is referred to as random I<sup>2</sup>C addressing. The TAS5086 also supports sequential I<sup>2</sup>C addressing. For write transactions, if a subaddress is issued, followed by data for that subaddress and the 15 subaddresses that follow, a sequential I<sup>2</sup>C write transaction has taken place, and the data for all 16 subaddresses is successfully received by the TAS5086. For I<sup>2</sup>C sequential write transactions, the subaddress then serves as the start address and the amount of data subsequently transmitted, before a stop or start is transmitted, determines how many subaddresses are written. As was true for random addressing, sequential addressing requires that a complete set of data be transmitted. If only a partial set of data is written to the last subaddress, the data for the last subaddress is discarded. However, all other data written is accepted; just the incomplete data is discarded.

## **SINGLE-BYTE WRITE**

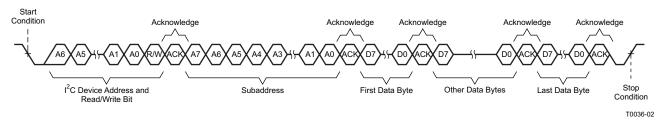

As shown is Figure 23, a single-byte data write transfer begins with the master device transmitting a start condition, followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write data transfer, the read/write bit must be set to 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the TAS5086 device responds with an acknowledge bit. Next, the master transmits the address byte or bytes corresponding to the TAS5086 internal memory address being accessed. After receiving the address byte, the TAS5086 again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte, the TAS5086 again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data write transfer.

Copyright © 2005–2008, Texas Instruments Incorporated

Figure 23. Single-Byte Write Transfer

#### MULTIPLE-BYTE WRITE AND INCREMENTAL MULTIPLE-BYTE WRITE

A multiple-byte data write transfer is identical to a single-byte data write transfer, except that multiple data bytes are transmitted by the master device to TAS5086 as shown in Figure 24. After receiving each data byte, the TAS5086 responds with an acknowledge bit.

Figure 24. Multiple-Byte Write Transfer

The I<sup>2</sup>C supports a special mode that permits I<sup>2</sup>C write operations to be broken up into multiple data write operations that are multiples of 4 data bytes. These are 6-, 10-, 14-, 18-, ..., etc., -byte write operations that are composed of a device address, read/write bit, and subaddress and any multiple of 4 bytes of data. This permits the system to write large register values incrementally without blocking other I<sup>2</sup>C transactions.

This feature is enabled by the *append* subaddress (0xFE) in the TAS5086. The append address, 0xFE, enables the TAS5086 to append an integer number of 4-, 8-, 12-, 16-, ... byte blocks of data to a register that was opened by a previous I<sup>2</sup>C register write operation, but has not received its complete number of data bytes.

When the correct number of bytes has been received, the TAS5086 starts processing the data.

The procedure to perform a multiple-byte write operation is as follows.

- 1. Start a normal I<sup>2</sup>C write operation by sending the device address, write bit, register subaddress, and an integer number of 4-byte data blocks. At the end of that sequence, a stop condition is sent.

- At this point the register has been opened. It then accepts the remaining data sent by one or more write operations, consisting of an integer number of 4-byte blocks. This data should be written to the append subaddress (0xFE).

- 2. At a later time, one or more append data transfers are performed to incrementally transfer the remaining number of bytes in sequential order to complete the register write operation. Each of these append operations is composed of the device address, write bit, append subaddress (0xFE), and an integer number of four bytes of data, followed by a stop condition.

- 3. The operation is terminated due to an error condition, and the data is flushed:

- If a new subaddress is written to the TAS5086 before the correct number of bytes has been written

- If a noninteger number of 4 bytes is written at the beginning or during any of the append operations

- If a read bit is sent

#### **SINGLE-BYTE READ**

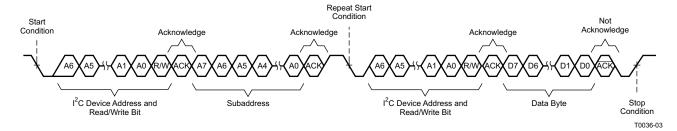

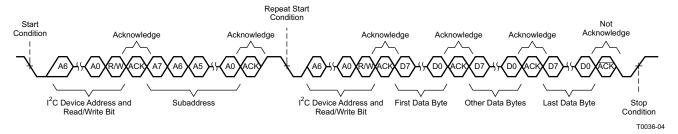

As shown in Figure 25, a single-byte data read transfer begins with the master device transmitting a start condition, followed by the I<sup>2</sup>C device address and the read/write bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte or bytes of the internal

memory address to be read. As a result, the read/write bit is set to a 0. After receiving the TAS5086 address and the read/write bit, the TAS5086 responds with an acknowledge bit. In addition, after sending the internal memory address byte or bytes, the master device transmits another start condition, followed by the TAS5086 address and the read/write bit again. This time, the read/write bit is set to 1, indicating a read transfer. After receiving the TAS5086 and the read/write bit, the TAS5086 again responds with an acknowledge bit. Next, the TAS5086 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not-acknowledge, followed by a stop condition, to complete the single-byte data read transfer.

Figure 25. Single-Byte Read Transfer

## **MULTIPLE-BYTE READ**

A multiple-byte data read transfer is identical to a single-byte data read transfer, except that multiple data bytes are transmitted by the TAS5086 to the master device as shown in Figure 26. Except for the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

Figure 26. Multiple-Byte Read Transfer

#### **COMMAND CHARACTERISTICS**

The TAS5086 has two groups of I<sup>2</sup>C commands. One set is commands that are designed specifically to be operated while audio is streaming and that have built-in mechanisms to prevent noise, clicks, and pops. The other set does not have this built-in protection.

## Commands that are designed to be adjusted while audio is streaming

- Master volume

- Master mute

- Individual channel volume

- Individual channel mute

Commands that the system executes without additional processing to prevent noise, clicks, or pops (in a number of cases this does not produce an audible click and pop)

- · Serial data interface format

- De-emphasis

- Sample rate conversion

- Input multiplexer

- Output multiplexer

- Biguads

- Downmix

- Channel delay

- Enable/disable automatic MCLK and data-rate detection

- Manual or automatic MCLK and data-rate setting

- Enable/disable dc blocking

- Hard/soft unmute from clock error

## SERIAL CONTROL INTERFACE REGISTER SUMMARY

Default values are in **bold**, table values "X" equals don't care and table values "—" equals an expansion of the table for detailed description of the respective bit.

| SUBADDRESS | REGISTER NAME                    | NO. OF<br>BYTES | CONTENTS                                | INITIALIZATION VALUE   |

|------------|----------------------------------|-----------------|-----------------------------------------|------------------------|

| 0x00       | Clock control register           | 1               | Description shown in subsequent section | 6C                     |

| 0x01       | Device ID register               | 1               | Description shown in subsequent section | 03                     |

| 0x02       | Error status register            | 1               | Description shown in subsequent section | 00                     |

| 0x03       | System control register 1        | 1               | Description shown in subsequent section | A0                     |

| 0x04       | Serial data interface register   | 1               | Description shown in subsequent section | 05                     |

| 0x05       | System control register 2        | 1               | Description shown in subsequent section | 60                     |

| 0x06       | Soft mute register               | 1               | Description shown in subsequent section | 00                     |

| 0x07       | Master volume                    | 1               | Description shown in subsequent section | FF (mute)              |

| 0x08       | Channel 1 vol                    | 1               | Description shown in subsequent section | 30 (0 dB)              |

| 0x09       | Channel 2 vol                    | 1               | Description shown in subsequent section | 30 (0 dB)              |

| 0x0A       | Channel 3 vol                    | 1               | Description shown in subsequent section | 30 (0 dB)              |

| 0x0B       | Channel 4 vol                    | 1               | Description shown in subsequent section | 30 (0 dB)              |

| 0x0C       | Channel 5 vol                    | 1               | Description shown in subsequent section | 30 (0 dB)              |

| 0x0D       | Channel 6 vol                    | 1               | Description shown in subsequent section | 30 (0 dB)              |

| 0x0E       | Volume control register          | 1               | Description shown in subsequent section | B1                     |

| 0x0F       |                                  |                 | RESERVED <sup>(1)</sup>                 |                        |

| 0x10       | Modulation limit register        | 1               | Description shown in subsequent section | 02                     |

| 0x11-0x17  |                                  |                 | RESERVED <sup>(1)</sup>                 |                        |

| 0x18       | PWM start register               | 1               | Description shown in subsequent section | 3F                     |

| 0x19       | Surround register                | 1               | Description shown in subsequent section | 00                     |

| 0x1A       | Split cap charge period register | 1               | Description shown in subsequent section | 18                     |

| 0x1B       | OSC_TRIM                         | 1               | Oscillator trim register                | 82                     |

| 0x1C       | BKNDERR register                 | 1               | BKNDErr Register                        | 05                     |

| 0x1D-0x1F  |                                  |                 | RESERVED <sup>(1)</sup>                 |                        |

| 0x20       | Input MUX register               | 4               | Description shown in subsequent section | 0x00, 0x01, 0x23, 0x45 |

| 0x21       | Downmix input MUX register       | 4               | Description shown in subsequent section | 0x00, 0x00, 0x40, 0x3F |

| 0x22       | AM tuned frequency               | 4               | Description shown in subsequent section | 0x00, 0x00, 0x00, 0x00 |

| 0x23       | ch6_bq[1]                        | 20              | b0[25:24] b0[(23:16], b0[15:8], b0[7:0] | 0x00, 0x80, 0x00, 0x00 |

|            |                                  |                 | b1[25:24] b1[23:16], b1[15:8], b1[7:0]  | 0x00, 0x00, 0x00, 0x00 |

|            |                                  |                 | b2[25:24] b2[23:16], b2[15:8], b2[7:0]  | 0x00, 0x00, 0x00, 0x00 |

|            |                                  |                 | a1[25:24] a1[23:16], a1[15:8], a1[7:0]  | 0x00, 0x00, 0x00, 0x00 |

|            |                                  |                 | a2[25:24] a2[23:16], a2[15:8], a2[7:0]  | 0x00, 0x00, 0x00, 0x00 |

| 0x24       | ch6_bq[2]                        | 20              | b0[25:24] b0[23:16], b0[15:8], b0[7:0]  | 0x00, 0x80, 0x00, 0x00 |

|            |                                  |                 | b1[25:24] b1[23:16], b1[15:8], b1[7:0]  | 0x00, 0x00, 0x00, 0x00 |

|            |                                  |                 | b2[25:24] b2[23:16], b2[15:8], b2[7:0]  | 0x00, 0x00, 0x00, 0x00 |

|            |                                  |                 | a1[25:24] a1[23:16], a1[15:8], a1[7:0]  | 0x00, 0x00, 0x00, 0x00 |

|            |                                  |                 | a2[25:24] a2[23:16], a2[15:8], a2[7:0]  | 0x00, 0x00, 0x00, 0x00 |

(1) Reserved registers should not be accessed.

Default values are in **bold**, table values "X" equals don't care and table values "-" equals an expansion of the table for detailed description of the respective bit.

| SUBADDRESS | REGISTER NAME     | NO. OF<br>BYTES | CONTENTS                                | INITIALIZATION VALUE   |

|------------|-------------------|-----------------|-----------------------------------------|------------------------|

| 0x25       | PWM MUX register  |                 | Description shown in subsequent section | 0x00, 0x32, 0x45, 0x10 |

| 0x26       | 1/G register      | 4               | x[25:24] x[23:16], x[15:8], x[7:0]      | 0x00, 0x80, 0x00, 0x00 |

| 0x27       |                   |                 | RESERVED <sup>(1)</sup>                 |                        |

| 0x28       | Scale register    | 4               | x[25:24] x[23:16], x[15:8], x[7:0]      | 0x00, 0x80, 0x00, 0x00 |

| 0x29-0xFD  |                   |                 | RESERVED <sup>(1)</sup>                 |                        |

| 0xFE       | Repeat subaddress | 4+4N            |                                         | 0x00, 0x00, 0x00, 0x00 |

| 0xFF       |                   |                 | RESERVED <sup>(1)</sup>                 |                        |

## **CLOCK CONTROL REGISTER (0x00)**

In the manual mode, the clock control register provides a way for the system microprocessor to update the data and clock rates, based on the sample rate and associated clock frequencies. In the autodetect mode, the clocks are determined automatically by the TAS5086. In this case, the clock control register contains the autodetected clock status as automatically detected. Bits D7–D5 select the sample rate. Bits D4–D2 select the MCLK frequency. Bit D1 selects the bit clock (SCLK) frequency. Bit D0 is used in manual mode only. In this mode, when the clocks are updated, a 1 must be written to D1 to inform the TAS5086 that the written clocks are valid.

Table 2. Clock Control Register (0x00)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                         |

|----|----|----|----|----|----|----|----|--------------------------------------------------|

| 0  | 0  | 0  | -  | -  | _  | -  | 1  | f <sub>S</sub> = 32-kHz sample rate              |

| 0  | 0  | 1  | -  | -  | -  | -  | -  | f <sub>S</sub> = 38-kHz sample rate              |

| 0  | 1  | 0  | ı  | -  | -  | -  | ı  | $f_S = 44.1$ -kHz sample rate                    |

| 0  | 1  | 1  | ı  | -  | -  | -  | ı  | f <sub>S</sub> = 48-kHz sample rate              |

| 1  | 0  | 0  | _  | _  | _  | _  | -  | $f_S = 88.2$ - kHz sample rate                   |

| 1  | 0  | 1  | 1  | _  | -  | _  | ı  | f <sub>S</sub> = 96-kHz sample rate              |

| 1  | 1  | 0  | 1  | _  | -  | _  | ı  | f <sub>S</sub> = 176.4-kHz sample rate           |

| 1  | 1  | 1  | ı  | -  | -  | -  | ı  | f <sub>S</sub> = 192-kHz sample rate             |

| -  | _  | -  | 0  | 0  | 0  | -  | ı  | MCLK frequency = $64 \times f_S^{(1)}$           |

| -  | _  | -  | 0  | 0  | 1  | -  | 1  | MCLK frequency = 128 x f <sub>S</sub>            |

| -  | _  | 1  | 0  | 1  | 0  | _  | ı  | MCLK frequency = 192 x f <sub>S</sub>            |

| _  | _  | _  | 0  | 1  | 1  | -  | -  | MCLK frequency = 256 × f <sub>S</sub>            |