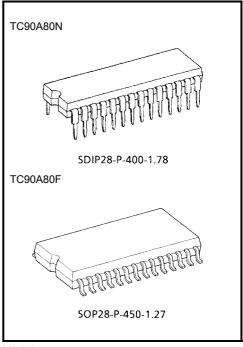

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC90A80N,TC90A80F

3-Line Digital Comb Filter for VCR, YNR/CNR, and Skew Correctors (NTSC)

The TC90A80N/F is a 3-line digital Y/C (luminance/chrominance) separation IC for VCR.

In addition to YNR and CNR used for noise reduction in the playback signal, the IC incorporates skew correctors for special playback. The IC is then suitable for processing S-VHS recorded playback signals.

#### **Features**

- TV format: NTSC (3.58)

- Dynamic comb filter

- YNR circuit

- CNR circuit

- Luminance signal non-linear vertical edge corrector (with coring function)

- Luminance signal horizontal frequency characteristic corrector (with coring function)

- Luminance signal line noise canceller

- Record/playback input switch circuit (switches between Y/C and Y inputs)

- Y and C input pins, independently one another (Y: sync tip clamp; C: center bias)

- Re-mixer circuit after Y/C sharpness processing

- Skew detector and correctors (NTSC ×5 Mode: in units of 0.2 H)

- PLL detector for switching frequencies (f<sub>sc</sub>, 2 f<sub>sc</sub>, 4 f<sub>sc</sub> and 8 f<sub>sc</sub> clock inputs)

- 8-bit 4  $f_{sc}$  AD converter (2 channels)

- 10-bit 8 f<sub>sc</sub> DA converter (2 channels)

- 1-H delay line (2 channels)

- I<sup>2</sup>C bus control

- I<sup>2</sup>C bus decode output pin (High/Low)

- 5-V single power operation

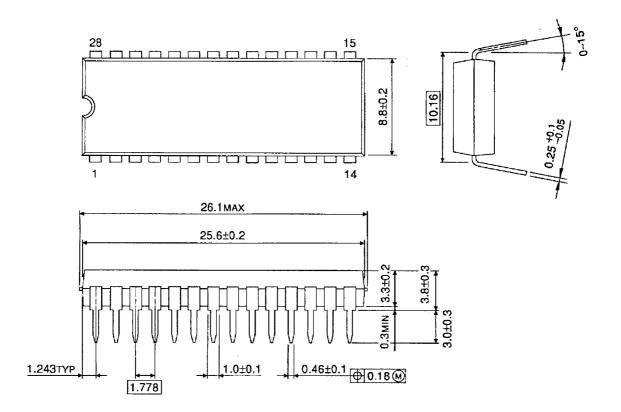

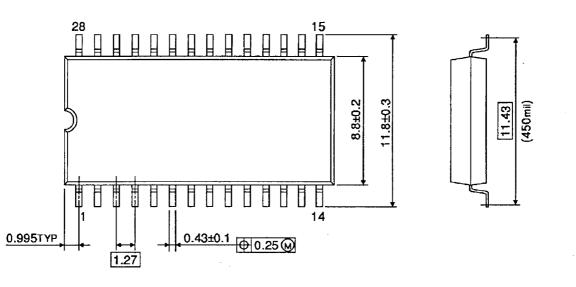

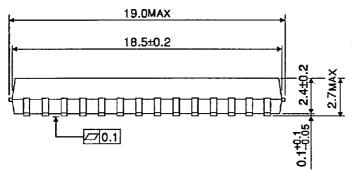

Weight

SDIP28-P-400-1.78: 1.7 g (typ.) SOP28-P-450-1.27: 0.8 g (typ.)

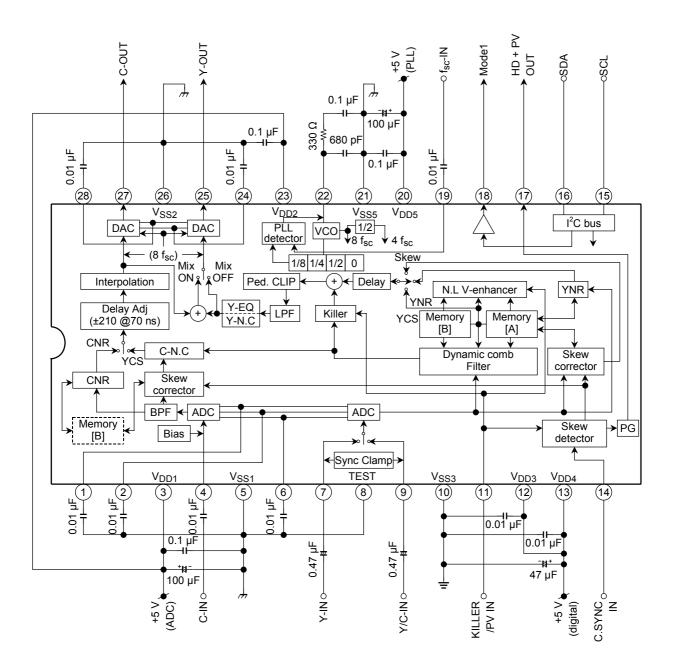

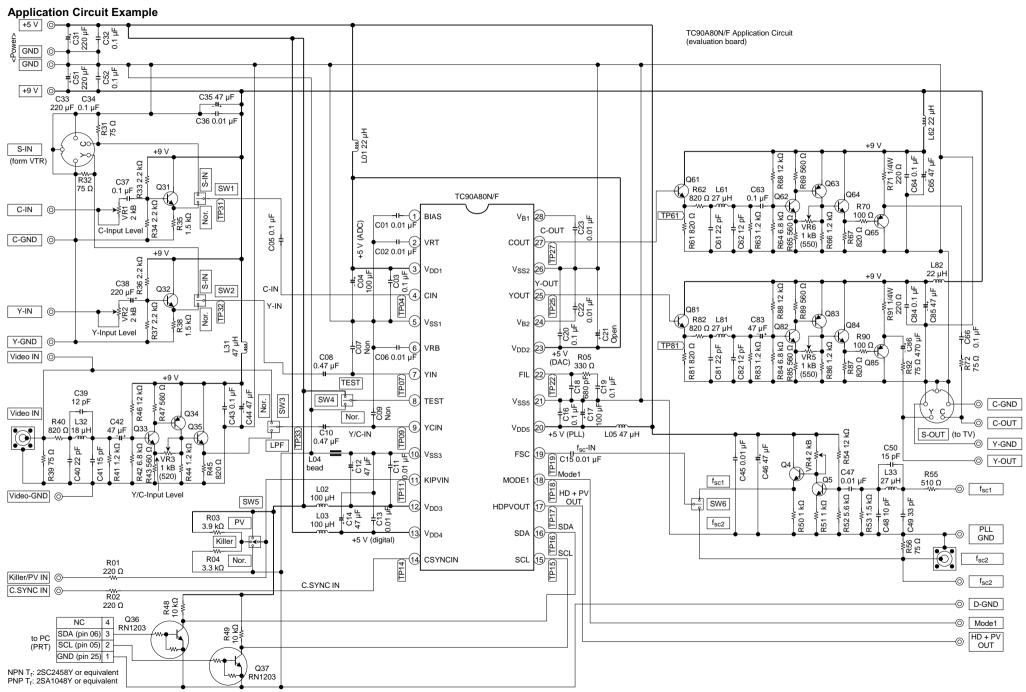

#### **Block Diagram**

#### **Pin Functions**

| Pin<br>No. | Pin Name         | Function                                                                                                                                                                                                                             | DC Level<br>(V)                                     | Interface Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | BIAS             | ADC bias pin Connect a $0.01$ - $\mu F$ capacitor between this pin and pin 5 (VSS1).                                                                                                                                                 | 1.3                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2          | VRT              | ADC bias pin  Sets upper limit of range D for ADC.  Connect a 0.01-µF capacitor between this pin and pin 5 (Vss1).  The output voltage is held at internal level.                                                                    | 3.16                                                | 20 Ω (1.14 kg)  |

| 3          | V <sub>DD1</sub> | ADC power supply pin (analog)  Apply the same voltage as that of pin 23 (V <sub>DD2</sub> ).                                                                                                                                         | 5.0                                                 | Internally connected to pin 23 (V <sub>DD2</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4          | CIN              | Chrominance signal input pin ( $I^2C$ Bus function: NR)  Because the signal is internally center-biased, it should be applied after cutting the DC component using a capacitor of around 0.01 $\mu$ F.                               | 2.5                                                 | 15 KD |

| 5          | V <sub>SS1</sub> | ADC GND pin (analog) Set the same voltage as that of pin 26 (V <sub>SS2</sub> ).                                                                                                                                                     | 0.0                                                 | Internally connected to pin 26 (V <sub>DD2</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6          | VRB              | ADC bias pin Sets lower limit of range D for ADC. Connect a 0.01-µF capacitor between this pin and pin 5 (Vss1). The output voltage is held at internal level.                                                                       | 1.83                                                | 6600 0 1.14 kD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7          | YIN              | Luminance signal input pin (I²C Bus function: NR)  Because sync tip clamp is internally used, the signal should be applied after cutting the DC component using a capacitor of around 0.47 µF.                                       | Sync Tip<br>NR Mode<br>: 1.86<br>YCS Mode<br>: 1.83 | 7 20 Ω 1 |

| 8          | TEST             | Pin for reset control and test control when shipping. Reset control: Applying pulse of 10 μs or longer while the pin is at High with power on resets all the I <sup>2</sup> C bus settings to 0. For normal use, set the pin to Low. | 0.0                                                 | 150 Ω<br>8  150 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

3

| Pin<br>No. | Pin Name         | Function                                                                                                                                                                                                                                                                                                                                                        | DC Level<br>(V)                                     | Interface Circuit                             |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------|

| 9          | YCIN             | Composite video signal input pin ( $I^2C$ Bus function: YCS) Because sync tip clamp is internally used, the signal should be applied after cutting the DC component using a capacitor of around 0.47 $\mu F$ .                                                                                                                                                  | Sync Tip<br>YCS Mode<br>: 1.86<br>NR Mode<br>: 1.83 | 20 Ω<br>20 Ω<br>20 Ω                          |

| 10         | V <sub>SS3</sub> | Logic and DRAM GND pin (digital) Separate digital $V_{SS}$ from analog $V_{SS}$ .                                                                                                                                                                                                                                                                               | 0.0                                                 | _                                             |

| 11         | KIPVIN           | Killer control and pseudo vertical pulse (PV) input pin (M or H polarity can be selected using I <sup>2</sup> C Bus.)  In Killer mode, Y/C separation, vertical enhancer, CNR, and YNR are halted. PV input: Vertical mask signal for detecting skew. Apply PV which is synchronous with input video signal. For normal use, or not in use, set the pin to Low. | 3-level<br>input                                    | 700 Ω 3.2 V<br>11 1.4 V                       |

| 12         | V <sub>DD3</sub> | Logic power supply pin (digital) Separate digital V <sub>DD</sub> from analog V <sub>DD</sub> .                                                                                                                                                                                                                                                                 | 5.0                                                 | _                                             |

| 13         | V <sub>DD4</sub> | DRAM power supply (digital) Separate digital $V_{DD}$ from analog $V_{DD}$ .                                                                                                                                                                                                                                                                                    | 5.0                                                 | _                                             |

| 14         | CSYNCIN          | Composite sync pulse input pin for detecting skew Apply sync separation pulse (positive polarity pulse) of the input video signal. When not in use, set to Low.                                                                                                                                                                                                 | -                                                   | 700 Ω<br>———————————————————————————————————— |

| 15         | SCL              | I <sup>2</sup> C bus clock input pin                                                                                                                                                                                                                                                                                                                            | -                                                   | 700 Ω<br>15                                   |

| 16         | SDA              | I <sup>2</sup> C bus data input/output pin                                                                                                                                                                                                                                                                                                                      | -                                                   | 700 Ω<br>ACK                                  |

| 17         | HDPVOUT          | Sync output pin  In Skew Correction Mode: Output can be selected as either HD pulse which is synchronous with output video signal or signal mixed with input PV.  In modes other than Skew Correction, drives out C Composite sync pulse. Use for later-stage circuit such as 3DNR.                                                                             | _                                                   | 17                                            |

| Pin<br>No. | Pin Name         | Function                                                                                                                                                                                                                                          | DC Level<br>(V)    | Interface Circuit                                  |

|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------|

| 18         | MODE1            | MODE1 output pin  High or Low output voltage signal can be selected using I <sup>2</sup> C bus. Use for controlling peripheral circuits.                                                                                                          | _                  | 18                                                 |

| 19         | FSC              | Clock input pin  Apply sine wave locked to the frequency of the input video burst signal. One of the four frequencies (f <sub>sc</sub> , 2f <sub>sc</sub> , 4f <sub>sc</sub> , and 8f <sub>sc</sub> ) can be selected using I <sup>2</sup> C bus. | 2.45               | 19 170 Ω W S NO KΩ                                 |

| 20         | $V_{DD5}$        | PLL power supply pin (analog)                                                                                                                                                                                                                     | 5.0                | _                                                  |

| 21         | V <sub>SS5</sub> | PLL GND pin (analog)                                                                                                                                                                                                                              | 0.0                | _                                                  |

| 22         | FIL              | VCO control pin Connect lag-lead filter between this pin and pin 21 (Vss5).                                                                                                                                                                       | 3.0                | 90 Ω (22) (100 Ω (4))                              |

| 23         | $V_{DD2}$        | DAC power supply pin (analog) Apply the same voltage as that of pin 3 (V <sub>DD1</sub> ).                                                                                                                                                        | 5.0                | Internally connected to pin 3 (V <sub>DD1</sub> ). |

| 24         | V <sub>B2</sub>  | DAC bias 2 pin Connect a $0.01$ - $\mu F$ capacitor between this pin and pin 26 ( $V_{SS2}$ ).                                                                                                                                                    | 3.4                | 24                                                 |

| 25         | YOUT             | Luminance signal output pin When Y/C Re-Mix Mode is selected using I <sup>2</sup> C bus, this pin drives out a composite video signal.                                                                                                            | Sync Tip<br>: 2.46 | © 004<br>0004<br>25                                |

| 26         | V <sub>SS2</sub> | DAC GND pin (analog) Set the same voltage as that of pin 5 (V <sub>SS1</sub> ).                                                                                                                                                                   | 0.0                | Internally connected to pin 5 (V <sub>SS1</sub> ). |

| Pin<br>No. | Pin Name        | Function                                                                                                                   | DC Level<br>(V) | Interface Circuit |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|

| 27         | COUT            | Chrominance signal output pin  When Y/C Re-Mix Mode is selected using I <sup>2</sup> C bus, this pin drives out no signal. | 3.7             | 27<br>C 0004      |

| 28         | V <sub>B1</sub> | DAC bias pin 1  Connect a 0.01-µF capacitor between this pin and pin 26 (V <sub>SS2</sub> ).                               | 1.6             | 28                |

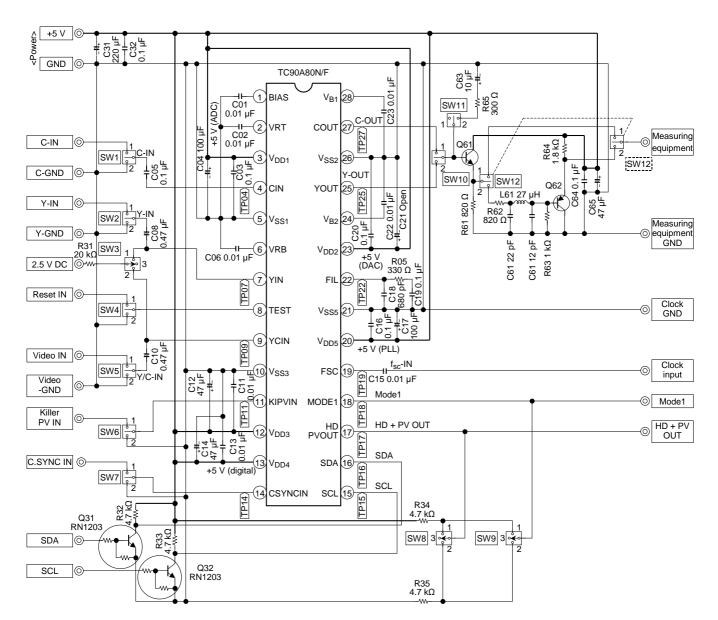

Note 1: Caution regarding external circuits (component allocation) for improving S/N and stabilizing operation:

Power supply pins are paired with GND pins. Read the section on Pin Functions and connect a ceramic capacitor and an electrolytic capacitor directly between power supply and GND pins.

Toshiba recommend using a capacitor of 0.1 µF or more between analog power supply and GND pins. (For digital pins, use a 0.01-µF capacitor.)

#### **IC Control Specifications**

- Functions and characteristics of this IC are set using the I<sup>2</sup>C bus.

- The data transfer format conforms to the Philips I<sup>2</sup>C bus format.

- When reset signal is applied, the following DATA bits are all cleared to 0.

- Data transfer format

| S | Slave address (8 bits) | Α | DATA1 | Α | DATA2 | Α | DATA3 | Α | DATA4 | Α | Р |

|---|------------------------|---|-------|---|-------|---|-------|---|-------|---|---|

Slave address: B4H S: Start condition, A: Acknowledgement, P: Stop condition

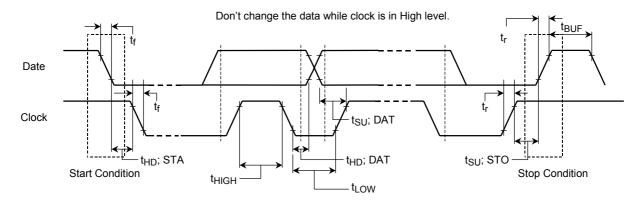

#### Outline of I<sup>2</sup>C bus format

I<sup>2</sup>C bus transfers data between ICs using two lines: data (SDA) and clock (SCL).

The I<sup>2</sup>C bus starts according to the start condition and ends according to the stop condition.

The start condition is satisfied if SDA changes from High to Low when SCL is High.

The stop condition is satisfied if SDA changes from Low to High when SCL is High.

The length of data to be transferred is 8 bits. Data are transferred via the SDA line. An acknowledge (ACK) bit is required after a data byte. The bus line must be pulled up to the power supply level using a resistor. When SCL is High, data must not be changed.

#### • I2C bus control signal timing

| Characteristics                                 | Symbol                | Min | Max  | Unit |

|-------------------------------------------------|-----------------------|-----|------|------|

| SCL clock frequency                             | f <sub>SCL</sub>      | 0   | 100  | kHz  |

| Hold time to satisfy start condition            | t <sub>HD</sub> ; STA | 4.0 | _    | μs   |

| SCL clock Low period                            | t <sub>LOW</sub>      | 4.7 | _    | μs   |

| SCL clock High period                           | t <sub>HIGH</sub>     | 4.0 | _    | μs   |

| Data hold time                                  | t <sub>HD</sub> ; DAT | 0   | 3.45 | μs   |

| Data setup time                                 | t <sub>SU</sub> ; DAT | 250 | _    | ns   |

| SDA/SCL signal rise time                        | t <sub>r</sub>        | _   | 1000 | ns   |

| SDA/SCL signal fall time                        | t <sub>f</sub>        | _   | 300  | ns   |

| Stop condition setup time                       | t <sub>SU</sub> ; STO | 4.0 | _    | μs   |

| Bus free time between stop and start conditions | t <sub>BUF</sub>      | 4.7 | _    | μs   |

Purchase of TOSHIBA  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Slave address: 1011010x

### I<sup>2</sup>C Bus Control Data List

## I<sup>2</sup>C Bus Control List

|       | D7                                    | D6                                     | D5                                  | D4                                  | D3                            | D2                                             | D1                                           | D0                                             |  |

|-------|---------------------------------------|----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------|------------------------------------------------|----------------------------------------------|------------------------------------------------|--|

|       | Function                              | Skew                                   |                                     | C-Delay                             |                               | D-Range                                        | Input Clock                                  |                                                |  |

| DATA1 | 0: YCS<br>1: NR                       | 0: OFF<br>1: ON                        | 000: ±0 ns<br>001: -70<br>010: -140 | 011: -210<br>100: ±0 ns<br>101: +70 | 110: +140<br>111: +210        | 0: 2 V <sub>p-p</sub><br>1: 1 V <sub>p-p</sub> | 00: f <sub>sc</sub><br>01: 2 f <sub>sc</sub> | 10: 4 f <sub>SC</sub><br>11: 8 f <sub>SC</sub> |  |

|       | CNR                                   | Gain                                   |                                     | CNR Lim.                            |                               | CNR Corr.                                      | Mode1                                        | Y-EQ/N.C f <sub>o</sub>                        |  |

| DATA2 | 00: OFF 10: 0.625<br>01: 0.5 11: 0.75 |                                        | 000: 1<br>001: 3<br>010: 5          | 011: 7<br>100: 9<br>101: 11         | 110: 13<br>111: 15            | 0: ON<br>1: OFF                                | 0: Low<br>1: High                            | 0: High<br>1: Low                              |  |

|       | Y-EQ                                  | (Gain                                  | Y-EQ/N                              | N.C Lim                             | YNR Corr.                     | Pulse M/H                                      | Sync Out                                     | Y/C Mix                                        |  |

| DATA3 | 00: OFF<br>01: 0.125                  | 10: 0.25<br>11: 0.5                    | 00: OFF<br>01: H2 (L4)              | 10: H4 (L8)<br>11: H8 (L14)         | 0: ON<br>1: OFF               | 0: PV<br>1: Killer                             | 0: HD<br>1: HD + PV                          | 0: OFF<br>1: ON                                |  |

|       | V-                                    | Emph Gain (Y0                          | CS)                                 | V                                   | -Emph N.L (YC                 | S)                                             | V-Emph Core (YCS)                            |                                                |  |

|       | 000: OFF<br>001: +0.25<br>010: +0.25  | 011: +0.50<br>100: +0.75<br>101: +1.00 | 110: +1.25<br>111: +1.50            | 000: 4<br>001: 8<br>010: 12         | 011: 16<br>100: 20<br>101: 24 | 110: 28<br>111: 32                             | 00: OFF<br>01: 1                             | 10: 2<br>11: 3                                 |  |

| DATA4 |                                       | YNR Gain (NR                           | )                                   |                                     | YNR Lim (NR)                  |                                                | YNR M                                        | ode (NR)                                       |  |

|       | 000: OFF<br>001: 0.125<br>010: 0.25   | 011: 0.375<br>100: 0.5<br>101: 0.625   | 110: 0.75<br>111: 0.875             | 000: 1<br>001: 3<br>010: 5          | 011: 7<br>100: 9<br>101: 11   | 110: 13<br>111: 15                             | 00: YNR-W<br>01: YNR-N                       | 10:<br>YCOMB-W<br>11:<br>YCOMB-N               |  |

## Description of I<sup>2</sup>C Bus Control

| (1)           | Function          | : Controls input signal and IC functions. (YCS: Y/C-IN $\rightarrow$ 3 line Y/C separation, NR: Y and C input independently $\rightarrow$ YNR, CNR) |

|---------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| (2)           | Skew              | : Controls skew correction. (OFF: normal mode, ON: Corrects skew every 0.2 H.)                                                                      |

| (3)           | C-Delay           | : Controls Y/C time. (Switches chroma signal delay time.   : Advances chroma signal.                                                                |

| (6)           | C Belay           | +: Delays chroma signal.)                                                                                                                           |

| (4)           | D-Range           | : Controls input/output gain. (2 Vp-p: 1 V input 2 V output, Gain = 6dB, 1 Vp-p: 1 V                                                                |

| (1)           | Divange           | input 1 V output, Gain = 0dB)                                                                                                                       |

| (5)           | Input Clock       | : Controls clock PLL. (Select input clock.)                                                                                                         |

| (6)           | CNR Gain          | : Controls CNR cyclic coefficient/subtraction gain. (OFF: Stops CNR. 0.75: Maximum                                                                  |

|               |                   | effect)                                                                                                                                             |

| (7)           | CNR Lim.          | : Controls the CNR limiter. (Limiter level when converting 100 IRE input.: $4 \approx -31 dB$ to $18 \approx -18 dB$ )                              |

| (8)           | CNR Corr.         | : Controls CNR correlation/non-correlation                                                                                                          |

|               |                   | ON: Controls CNR correlation/non-correlation. $\rightarrow$ Low vertical color misalignment                                                         |

|               |                   | OFF: Maximum $\rightarrow$ effect with vertical color misalignment                                                                                  |

| (9)           | Mode1             | : Controls parallel output. (Low: Drives out voltage approx. VSS. High: Drives out voltage approx. VDD.)                                            |

| (10)          | Y-EQ fo           | : Corrects Y frequency characteristic and controls Y-NC bottom frequency. (high: 4/3                                                                |

|               | •                 | $f_{SC}$ , low: $f_{SC}$ )                                                                                                                          |

| (11)          | Y-EQ Gain         | : Controls Y frequency characteristic correction addition gain. (OFF: Stops frequency characteristic correction. 0.5: Corrects by +3dB at 3 MHz.)   |

| (12)          | Y-EQ/N.C Lim      | : Controls Y frequency characteristic correction coring level and Y-NC limiter. (OFF:                                                               |

|               | •                 | N.C OFF, H*: Limiter level when Y-EQ $f_0$ = high, L*: Limiter level when Y-EQ $f_0$ =                                                              |

|               |                   | low, When converting 100 IRE input, limiter levels are as follows.2: -37dB, 4: -31dB,                                                               |

|               |                   | 8: -25dB, 14: -20dB)                                                                                                                                |

| (13)          | YNR Corr.         | : Controls YNR correlation/non-correlation                                                                                                          |

|               |                   | ON: Controls YNR correlation/non-correlation $\rightarrow$ Low Y vertical color misalignment                                                        |

|               |                   | OFF: Maximum effect → with Y vertical color misalignment                                                                                            |

| (14)          | Pulse Middle/High | : Controls High pulse input polarity. (PV: PV with M/H and Killer with Middle/Low, Killer: Killer with M/H and PV with M/L)                         |

|               |                   | PV: Used for vertical-masking PLL for detecting skew and driving out HD + PV                                                                        |

|               |                   | when compensating skew.                                                                                                                             |

|               |                   | Killer: Used for controlling separation Off, V-Emph Off in YCS Mode, and YNR/CNR                                                                    |

|               |                   | Off in NR Mode.                                                                                                                                     |

| (15)          | Sync Out          | : Controls pulse output in Skew Correction Mode. (HD: Drives out HD which is                                                                        |

|               |                   | synchronous with output signal. HD + PV: Mixes PV in HD which is synchronous                                                                        |

|               |                   | with to output signal.) HD lock phase is not held (varies from 500 ns to 600 ns).                                                                   |

|               |                   | In modes other than Skew Correction, drives out input C.SYN after delaying approx.                                                                  |

|               |                   | 560 ns.                                                                                                                                             |

| (16)          | Y/C Mix           | : Controls Y/C mix output. (OFF: Drives out separated Y and C. ON: Drives out mixed                                                                 |

| (- <b>-</b> ) |                   | Y and C from the Y output pin. The C output pin is mute.)                                                                                           |

|               | _                 | Controls vertical enhancer gain. (OFF: Enhancer Off. +1.5: Maximum effect)                                                                          |

|               |                   | Controls vertical enhancer non-linear point. (4: Low effect, 32: Maximum effect)                                                                    |

| (19)          | V-Emph Core (YCS) | Controls vertical enhancer coring. (OFF: Coring Off. 3: Emphasizes non correlation                                                                  |

| (20)          | VAID (C : (AID)   | of approx. 15 mV or more.)                                                                                                                          |

| (20)          | YNR Gain (NR)     | : Controls YNR cyclic coefficient/subtraction gain. (OFF: Stops YNR. 0.875: Maximum                                                                 |

| (01)          | YNR Lim (NR)      | effect) : Controls the VNP limiter (Limiter level when converting 100 IPF input: 1 ~                                                                |

| (21)          | ING LIM (NK)      | : Controls the YNR limiter. (Limiter level when converting 100 IRE input.: 1 $\approx$ $-43$ dB $\approx$ 15 $\approx$ $-19$ dB)                    |

| (99)          | YNR Mode (NR)     | -43dB~15 ≈ -19dB)<br>: Controls YNR and Y-COMB bandwidths. (*-W: Wideband, *-N: Narrowband)                                                         |

|               |                   | f DATA4 D7 to DATA4 D0 vary according to the setting of DATA1 D7 (function).)                                                                       |

| (140)         | controls of       | Diffil D. to Diffil Do vary according to the setting of Diffil Dr (talledoll).)                                                                     |

|               |                   |                                                                                                                                                     |

#### **Functions**

| Bus Setting          | Bus Setting |             | Function    |       |              |       |        |             |            |      |        |           |             |            |           |           |     |   |   |

|----------------------|-------------|-------------|-------------|-------|--------------|-------|--------|-------------|------------|------|--------|-----------|-------------|------------|-----------|-----------|-----|---|---|

| Function             | Skew        | Y/C<br>Sep  | C-<br>Delay | Drang | CK<br>Select | CNR   | YNR    | Y-<br>EQ/NC | V-<br>Emph | Skew | Killer | P-<br>M/H | Sync output | Y/C<br>MIX | Y-<br>OUT | C-<br>OUT |     |   |   |

|                      | OFF         | 3 Line      | 0           | 0     | 0            | C-N.C | ×      | 0           | 0          | ×    | 0      | 0         | C Suno      | OFF        | Υ         | С         |     |   |   |

| YCS (composite video | OFF         | Comb<br>Sep |             |       | 0            |       | -N.C × | 5           | O          | ^    | O      |           | C.Sync      | ON         | Y/C       | Mute      |     |   |   |

| signal input)        | ON          | ON          | ON          | ON    | BPF          | 0     | 0      | 0           |            | ×    | 0      | 0         | 0           | 0          | 0         | HD·PV     | OFF | Υ | С |

|                      |             | Sep         | O           | Ŭ     | O            | C-N.C | (      | O           | )          | )    | )      | )         | TID'F V     | ON         | Y/C       | Mute      |     |   |   |

|                      | OFF         | ×           | 0           | 0     | 0            | 0     | 0      | 0           | ×          | ×    | 0      | 0         | C.Sync      | OFF        | Y         | С         |     |   |   |

| NR<br>(Y and C input | OIT         | (           | O           | )     | O            | )     | )      | O           | (          | (    | )      | )         | C.Syric     | ON         | Y/C       | Mute      |     |   |   |

| independently)       | ON          | ¥           | 0           | 0     | 0            |       | ×      | 0           | ×          | 0    | 0      | 0         | HD·PV       | OFF        | Υ         | С         |     |   |   |

|                      | ON          | 1 ×         | J           | 0     | U            | C-N.C | ^      | J           |            | 0    | J      | )         | IID.E.A     | ON         | Y/C       | Mute      |     |   |   |

O: Specified, x: Not specified

#### **Description of Functions**

- (1) 3-line Y/C separation circuit (VTR Record Mode)

- Provides clear Y and C separation using a dynamic comb filter, which logically extracts the chrominance signal, based on the result of detecting vertical 3-line non correlation using two 1-H delay lines. Also incorporates a vertical edge enhancer with coring function, which produces a clearer record signal with suppressed noise.

- (2) YNR and CNR circuits (VTR Playback Mode)

Independently incorporates cyclic noise reduction using 1-H delay lines for Y and C, effectively reducing vertical non-correlation noise in the playback signal.

- (3) Skew corrector (Special Playback Mode for VHS VTR  $\times 5$  speed videotape)

- From composite sync pulse signal (sync separation output) detects horizontal skew in units of 0.2 H (×2 = 0.4 H before and after Cue/Rev noise bar) generated at special playback of VHS VTR ×5 speed videotape. Using the detection result, automatically corrects horizontal skew included in the input playback video signal by switching the delay time for line memory.

- This function can be used for both composite video signals and independently applied Y and C signals.

- 1) Pseudo vertical (PV) signal and composite signal necessary for detecting skew Based on the reference signal of the horizontal frequency generated from the input composite sync signal, detects the position of input sync signal in units of 0.2 H. Because skew is detected due to the noise included in the input composite signal, apply the composite sync signal from which noise is reduced to some extent at sync separation (no filter in the IC).

- Note that erroneous skew detection around the period where vertical sync signal is included can be prevented by halting skew detection and by setting PLL to the  $f_h$  as reference during the PV pulse period. So, apply pseudo vertical signal.

- 2) Supplementary function: pin 17 (HDPVOUT)

- In Skew Correction Mode, pin 17 drives out the HD pulse (width: approx. 4  $\mu$ s) which synchronizes with the video signal after skew correction; in modes other than Skew Correction, pin 17 drives out the input composite sync signal. Pin 17 can also be used for output with the input PV mixed using the I<sup>2</sup>C bus (in Skew Correction Mode only). Use pin 17 for later-stage circuit such as 3DNR. Note, however, that since the HD lock position and jitter performance are not designed for high precision, do not use pin 17 directly for circuits requiring high precision.

- 3) Recommended use conditions (eg, search speed)

- Since the skew amount is not the same for Cue/Rev with ×5 speed tape, depending on the search speed, after skew correction, horizontal synchronization may become inconsistent at junctions between fields. As a result, the time for each field differs and vertical synchronization degrades.

- To avoid this phenomenon, it is necessary to select a search speed where four types of skew comprise a cycle during a 1-V pulse period (excluding PV pulse period). Consider a search speed with no or not much degradation of vertical synchronization, paying attention to the position of the noise bar. (Example): In  $\times 11$  Cue Mode, skew for the 1-V pulse period consists of Skew  $0~H \rightarrow noise \rightarrow skew 0.4~H$

- $\rightarrow$  noise  $\rightarrow$  skew 0.8 H  $\rightarrow$  noise  $\rightarrow$  skew 0.2 H  $\rightarrow$  noise  $\rightarrow$  skew 0.6 H  $\rightarrow$  noise  $\rightarrow$  skew 0 H. Where, consistency of horizontal synchronization is maintained. Degradation of vertical synchronization can also be made less conspicuous visually by increasing the search speed.

#### Maximum Rating (Ta = 25°C)

| Characteri                             | stics                    | Symbol           | Rating                           | Unit  |  |

|----------------------------------------|--------------------------|------------------|----------------------------------|-------|--|

| Supply voltage                         |                          | $V_{DD}$         | V <sub>SS</sub> + 6.0            | V     |  |

| Input voltage                          |                          | $V_{IN}$         | $V_{SS}$ – 0.3 to $V_{DD}$ + 0.3 | V     |  |

| Potential difference be<br>supply pins | etween power<br>(Note 2) | $V_{DG}$         | 0.4                              | ٧     |  |

| Power dissipation                      | TC90A80N                 | D <sub>n</sub>   | 900                              | mW    |  |

| (Note 3)                               | TC90A80F                 | $P_{D}$          | 600                              | IIIVV |  |

| Storage temperature                    |                          | T <sub>stg</sub> | -55 to +125                      | °C    |  |

Note 2: Connect pin 3 to pin 23. The potential difference among all power supply pins, 3 (23), 12, 13, and 20, must not exceed 0.4 V.

The potential difference among VSS pins 5, 10, 21, and 26 must not exceed 0.01 V.

Note 3:  $Ta = 75^{\circ}C$  for TC90A80F mounted on a PCB (70 mm × 70 mm × 1.6 mm)

#### **Recommended Operating Conditions**

| Characteristics                                                   | Symbol           | Min  | Тур. | Max             | Unit |

|-------------------------------------------------------------------|------------------|------|------|-----------------|------|

| Supply voltage                                                    | $V_{DD}$         | 4.75 | 5.00 | 5.25            | V    |

| Potential difference between pins 3 and 23 (Note 4)               | V <sub>DG1</sub> | _    | 0    | 0.04            | V    |

| Potential difference among power supply pins 3,12, 13, and 20     | $V_{DG2}$        | _    | 0    | 0.15            | V    |

| Potential difference among V <sub>SS</sub> pins 5, 10, 21, and 26 | V <sub>SG</sub>  | _    | 0    | 0.01            | V    |

| Input voltage                                                     | V <sub>IN</sub>  | 0    | _    | V <sub>DD</sub> | V    |

| Operating temperature                                             | T <sub>opr</sub> | -10  | _    | 75              | °C   |

Note 4: Since power supply pins 3 and 23 are connected in the IC, supply power to them at the same voltage. If there is a large potential difference between the pins, a large current flows through the IC causing degradation or damage due to heat stress.

Maximum ratings: A set of specified parameter values which must not be exceeded during operation, even for an instant. If any of these limit values is exceeded during operation, it causes permanent damage to the TC90A80N/F. Therefore, care must be exercised that the TC90A80N/F operates within the specified ranges.

Recommended operating conditions: Minimum, typical and maximum values for key operating parameters such as supply voltage, DC voltage and operating temperature. Ensuring that the parameter values remain within these specified ranges during operation will help to ensure that the integrity of the TC90A80N/F is not compromised. When designing video equipment, be aware that the TC90A80N/F can function within the recommended operating ranges.

#### **Electrical Characteristics**

DC Characteristics (Ta = 25°C,  $V_{DD}$  = 5.00 V, clock input: 3.579545 MHz, 0.5  $V_{p-p}$ ,  $I^2C$  BUS: according to test conditions)

| Observatoriation         | Pin                                           | Pin             | 0                | NA:             | т    |                 | 1.1-21   | -                                                                                                                                                                                                                                                                                                         | Test Condi | tions (Rem   | arks)       |                                                                                 |

|--------------------------|-----------------------------------------------|-----------------|------------------|-----------------|------|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|-------------|---------------------------------------------------------------------------------|

| Characteristics          | No.                                           | Name            | Symbol           | Min             | Тур. | Max             | Unit     | I <sup>2</sup> C bus setup                                                                                                                                                                                                                                                                                | DATA1      | DATA2        | DATA3       | DATA4                                                                           |

| Power supply             | 3, 12,<br>13,<br>20, 23                       | $V_{DD}$        | I <sub>DD</sub>  | 60              | 85   | 105             | mA       | • Input signal : • Test content :                                                                                                                                                                                                                                                                         | Measure t  | he total cui |             | ver .                                                                           |

|                          | 1                                             | BIAS            | V <sub>1</sub>   | 0.9             | 1.3  | 1.7             | V        | I <sup>2</sup> C bus setup                                                                                                                                                                                                                                                                                | 0 0        | 0 0          | 0 0         | 0 0                                                                             |

|                          | 2                                             | VRT             | V <sub>2</sub>   | 3.02            | 3.16 | 3.30            | V        | • Input signal :                                                                                                                                                                                                                                                                                          | Not apply  | to pins 4, 7 | 7, and 9.   | <u> </u>                                                                        |

|                          | 4                                             | CIN             | V <sub>4</sub>   | 2.4             | 2.5  | 2.6             | V        | • Test content :                                                                                                                                                                                                                                                                                          | Measure t  | he DC volt   | age of thos | se pins.                                                                        |

|                          | 6                                             | VRB             | V <sub>6</sub>   | 1.69            | 1.83 | 1.97            | V        |                                                                                                                                                                                                                                                                                                           |            |              |             |                                                                                 |

|                          | 7                                             | YIN             | V <sub>7</sub>   | 1.69            | 1.83 | 1.97            | V        |                                                                                                                                                                                                                                                                                                           |            |              |             |                                                                                 |

| D'a college              | 9                                             | YCIN            | V <sub>9</sub>   | 1.72            | 1.86 | 2.00            | V        |                                                                                                                                                                                                                                                                                                           |            |              |             |                                                                                 |

| Pin voltage              | 19                                            | FSC             | V <sub>19</sub>  | 2.00            | 2.45 | 2.90            | V        |                                                                                                                                                                                                                                                                                                           |            |              |             |                                                                                 |

|                          | 22                                            | FIL             | V <sub>22</sub>  | 1.8             | 3.0  | 4.2             | V        |                                                                                                                                                                                                                                                                                                           |            |              |             |                                                                                 |

|                          | 24                                            | V <sub>B2</sub> | V <sub>24</sub>  | 3.0             | 3.4  | 3.8             | V        |                                                                                                                                                                                                                                                                                                           |            |              |             |                                                                                 |

|                          | 25                                            | YOUT            | V <sub>25</sub>  | 2.37            | 2.5  | 2.63            | V        | -                                                                                                                                                                                                                                                                                                         |            |              |             |                                                                                 |

|                          | 27                                            | COUT            | V <sub>27</sub>  | 3.52            | 3.7  | 3.88            | V        | -                                                                                                                                                                                                                                                                                                         |            |              |             |                                                                                 |

|                          | 28                                            | V <sub>B1</sub> | V <sub>28</sub>  | 1.2             | 1.6  | 2.0             | V        | -                                                                                                                                                                                                                                                                                                         |            |              |             |                                                                                 |

|                          |                                               |                 | $V_{IML}$        | V <sub>SS</sub> | _    | 1.0             | V        | I <sup>2</sup> C bus setup                                                                                                                                                                                                                                                                                |            |              |             |                                                                                 |

| 3-level input<br>voltage | 11: KIPVIN                                    |                 | V <sub>IMM</sub> | 1.8             | _    | 2.8             | <b>V</b> | V <sub>IML</sub> : Normal operation  V <sub>IMM</sub> : Stops Y/C separation (drives out composit video signal to pin 25).  V <sub>IMH</sub> : Receives PV                                                                                                                                                |            |              |             |                                                                                 |

|                          |                                               |                 | V <sub>IMH</sub> | 3.6             | _    | V <sub>DD</sub> | ٧        | (drives out High (V <sub>OH</sub> ) to pin 17).  Operations of V <sub>IMM</sub> and V <sub>IMH</sub> are inverted by DATA = 1 of the I <sup>2</sup> C bus settings.  To support high-speed pulse input, the circuit must high hysteresis                                                                  |            |              |             |                                                                                 |

|                          |                                               |                 | V <sub>IH</sub>  | 4               | _    | V <sub>DD</sub> | V        | I <sup>2</sup> C bus setup                                                                                                                                                                                                                                                                                | 0 0        | 0 2          | 0 0         | 0 0                                                                             |

| 2-level input<br>voltage | 8 : TEST<br>14: CSYNCIN<br>15: SCL<br>16: SDA |                 | V <sub>IL</sub>  | V <sub>SS</sub> | _    | 1               | V        | Test content: Apply DC voltage to pins 8, 16. Change the DC voltage the point where High/Low let to those pins by monitoring change on pins 17 and 18. input bottom voltage of the and 16.  VIH: Apply reset signal, composite sync si High level.  VIL: Apply reset signal, composite sync si Low level. |            |              |             | I check<br>is applied<br>DC<br>sure the<br>8, 14, 15<br>I, I <sup>2</sup> C bus |

|                | V <sub>OH</sub> 4.6 — V <sub>DD</sub> | V             | I <sup>2</sup> C bus setup | 0 0             | 0 0 | 0 0         | 0 0 |                                                                                                                                                                                                                               |                   |                          |             |                   |  |  |

|----------------|---------------------------------------|---------------|----------------------------|-----------------|-----|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|-------------|-------------------|--|--|

|                |                                       |               | VOH                        | 4.0             |     | <b>∀</b> DD | V   | I <sup>2</sup> C bus setup                                                                                                                                                                                                    | 0 0               | 0 2                      | 0 0         | 0 0               |  |  |

| Output voltage | 17: HC<br>18: MC                      | PVOUT<br>DDE1 | V <sub>OL</sub>            | V <sub>SS</sub> | _   | 0.4         | V   | Test content: Measure the output voltage on pins 17 and 18 when DC is applied with a 4.7-kΩ resistor.  VOH: Connects a 4.7-kΩ resistor between pin 17/18 and GND.  VOL: Connects a 4.7-kΩ resistor between pin 17/18 and VDD. |                   |                          |             |                   |  |  |

|                |                                       |               |                            |                 |     |             |     | I <sup>2</sup> C bus setup                                                                                                                                                                                                    | 0 0               | 0 0                      | 0 0         | 0 0               |  |  |

|                | 16                                    | 6 SDA         | V <sub>ACK</sub>           | V <sub>SS</sub> | _   | 0.4         | V   | Test content :                                                                                                                                                                                                                |                   | he ACK ou<br>lied with a |             |                   |  |  |

|                |                                       |               |                            |                 | 1   |             | 1   | Connect a 4.7-k                                                                                                                                                                                                               | $\Omega$ resistor | between p                | in 16 and \ | / <sub>DD</sub> . |  |  |

#### **AC Characteristics**

## Luminance signal input/output characteristics (Ta = 25°C, $V_{DD}$ = 5.00 V, clock input: 3.579545 MHz, 0.5 $V_{p-p}$ , $I^2C$ bus: according to test conditions)

| •                         |                  |      |      |      |        |                            |                                                                                                         |                                        |                                          |             |  |  |

|---------------------------|------------------|------|------|------|--------|----------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|-------------|--|--|

|                           | Symbol           | N 4: | Т    | Mari | I lada |                            | Test Condi                                                                                              | tions (Rem                             | narks)                                   |             |  |  |

| Characteristics           | Syllibol         | Min  | Тур. | Max  | Unit   | I <sup>2</sup> C bus setup | DATA1                                                                                                   | DATA2                                  | DATA3                                    | DATA4       |  |  |

| Recommended input level   | V <sub>YIN</sub> | _    | 1.0  | 1.3  | V      | I <sup>2</sup> C bus setup | 0 0                                                                                                     | 0 0                                    | 0 0                                      | 0 0         |  |  |

|                           |                  |      |      |      |        | • Input signal :           | Apply whi                                                                                               | te 100% si                             | gnal to pin                              | s 7 and 9.  |  |  |

|                           |                  |      |      |      |        | I <sup>2</sup> C bus setup | 0 0                                                                                                     | 0 0                                    | 0 0                                      | 0 0         |  |  |

| Low-frequency gain        | GY               | 5.5  | 6.0  | 6.5  | dB     | • Input signal :           | Apply whi                                                                                               | te 100% si                             | ignal at 1-∖                             | /p-p to pin |  |  |

|                           |                  |      |      |      |        | • Test content:            | Compare input leve                                                                                      |                                        | tput level                               | with pin 9  |  |  |

|                           |                  |      |      |      |        | I <sup>2</sup> C bus setup | 0 0                                                                                                     | 0 0                                    | 0 0                                      | 0 0         |  |  |

|                           |                  |      |      |      |        | • Input signal             | : Apply 1-\                                                                                             | /p-p, 2.5-V                            | DC offset                                | sine        |  |  |

| Comb characteristic       | Ycom             | 40   | 45   | _    | dB     |                            | wave to p                                                                                               | oin 9.                                 |                                          |             |  |  |

|                           |                  |      |      |      |        | Test content               | Measure                                                                                                 | gain differ                            | nge input fi<br>ence betwe<br>5.579545 M | en          |  |  |

|                           |                  |      |      |      |        | I <sup>2</sup> C bus setup | 0 0                                                                                                     | 0 0                                    | 0 0                                      | 0 0         |  |  |

|                           |                  |      |      |      |        | Input signal               | : Apply 1-\                                                                                             | /p-p, 2.5-V                            | DC offset                                | sine        |  |  |

| Frequency characteristic  | FY               | -2   | -1   | 0    | dB     | wave to pin 9.             |                                                                                                         |                                        |                                          |             |  |  |

|                           |                  | _    |      |      |        | Test content               | input freq                                                                                              | uency. Me                              | ller Mode.<br>easure gain<br>0.5 MHz a   |             |  |  |

| Differential error        | L                | -1   | 0    | +1   | LSB    | (reference valu            | e)                                                                                                      |                                        |                                          |             |  |  |

| Integral error            | В                | -3   | 0    | +3   | LSB    | (reference value)          |                                                                                                         |                                        |                                          |             |  |  |

|                           |                  |      |      |      |        | I <sup>2</sup> C bus setup | 0 0                                                                                                     | 0 0                                    | 0 0                                      | 0 0         |  |  |

| Output impedance          | Zy               | 250  | 400  | 700  | Ω      | Input signal               | : Input 1-V<br>pin 9.                                                                                   | p-p, 15-kH                             | z square w                               | ave to      |  |  |

|                           | _,               |      |      |      |        | • Test content             | t: Calculate output impedance, AC applied with/without 300-Ω resistor connected between pin 25 and GND. |                                        |                                          |             |  |  |