INTEGRATED CIRCUITS

Product specification Supersedes data of 1995 April 27 File under Integrated Circuits, IC02 1996 Mar 21

#### **Product specification**

## 10-bit high-speed low-power analog-to-digital converter

#### FEATURES

- 10-bit resolution

- Sampling rate up to 80 MHz

- DC sampling allowed

- One clock cycle conversion only

- High signal-to-noise ratio over a large analog input frequency range (9.3 effective bits at 4.43 MHz full-scale input at  $f_{clk} = 80$  MHz)

- No missing codes guaranteed

- In range (IR) TTL output

- TTL compatible digital inputs and outputs

- Low-level AC clock input signal allowed

- External reference voltage regulator

- Power dissipation only 380 mW (typical)

- Low analog input capacitance, no buffer amplifier required

- No sample-and-hold circuit required.

QUICK REFERENCE DATA

### APPLICATIONS

High-speed analog-to-digital conversion for:

- Video data digitizing

- Radar pulse analysis

- Transient signal analysis

- High energy physics research

- $\Sigma\Delta$  modulators

- Medical imaging.

### **GENERAL DESCRIPTION**

The TDA8762A is a 10-bit high-speed analog-to-digital converter (ADC) for professional video and other applications. It converts the analog input signal into 10-bit binary-coded digital words at a maximum sampling rate of 80 MHz. All digital inputs and outputs are TTL compatible, although a low-level sine wave clock input signal is allowed.

| SYMBOL                | PARAMETER                    | CONDITIONS                                | MIN. | TYP.  | MAX. | UNIT |

|-----------------------|------------------------------|-------------------------------------------|------|-------|------|------|

| V <sub>CCA</sub>      | analog supply voltage        |                                           | 4.75 | 5.0   | 5.25 | V    |

| V <sub>CCD</sub>      | digital supply voltage       |                                           | 4.75 | 5.0   | 5.25 | V    |

| V <sub>cco</sub>      | output stages supply voltage |                                           | 4.4  | 5.0   | 5.25 | V    |

| I <sub>CCA</sub>      | analog supply current        |                                           | -    | 29    | 36   | mA   |

| I <sub>CCD</sub>      | digital supply current       |                                           | -    | 24    | 30   | mA   |

| I <sub>CCO</sub>      | output stages supply current | $C_L = 15 \text{ pF}; \text{ ramp input}$ | -    | 23    | 30   | mA   |

| INL                   | integral non-linearity       | f <sub>clk</sub> = 80 MHz; ramp input     | -    | ±0.75 | ±1.5 | LSB  |

| DNL                   | differential non-linearity   | f <sub>clk</sub> = 80 MHz; ramp input     | _    | ±0.3  | ±0.7 | LSB  |

| f <sub>clk(max)</sub> | maximum clock frequency      |                                           |      |       |      |      |

|                       | TDA8762AM/6                  |                                           | 60   | _     | -    | MHz  |

|                       | TDA8762AM/8                  |                                           | 80   | -     | -    | MHz  |

| P <sub>tot</sub>      | total power dissipation      |                                           | -    | 380   | 500  | mW   |

### ORDERING INFORMATION

| TYPE        |        | PACKAGE                                         |          | SAMPLING        |

|-------------|--------|-------------------------------------------------|----------|-----------------|

| NUMBER      | NAME   | DESCRIPTION                                     | VERSION  | FREQUENCY (MHz) |

| TDA8762AM/6 | SSOP28 | plastic shrink small outline package; 28 leads; | SOT341-1 | 60              |

| TDA8762AM/8 | SSOP28 | body width 5.3 mm                               | SOT341-1 | 80              |

## 10-bit high-speed low-power analog-to-digital converter

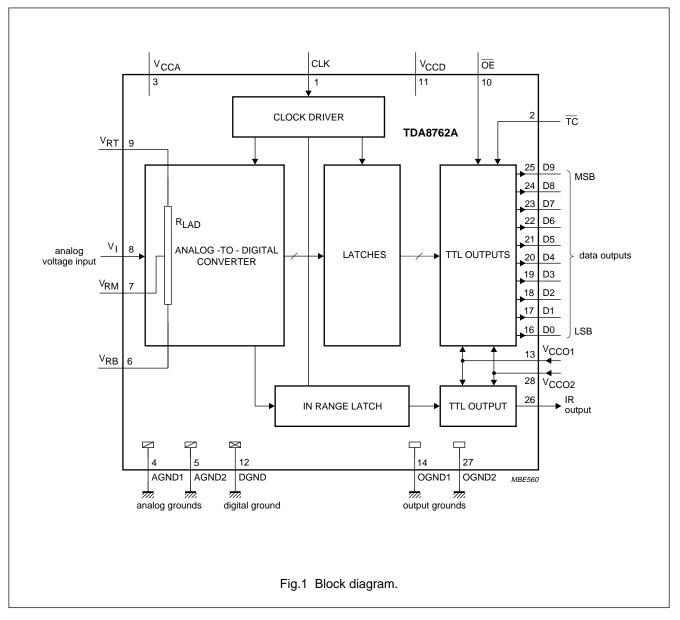

### **BLOCK DIAGRAM**

### Product specification

TDA8762A

## 10-bit high-speed low-power analog-to-digital converter

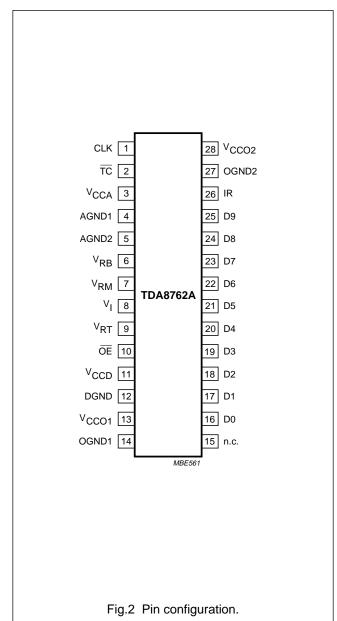

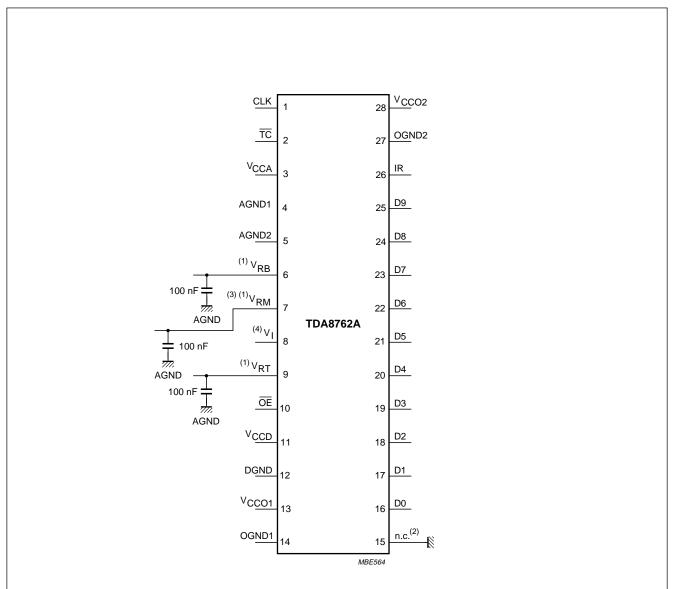

### PINNING

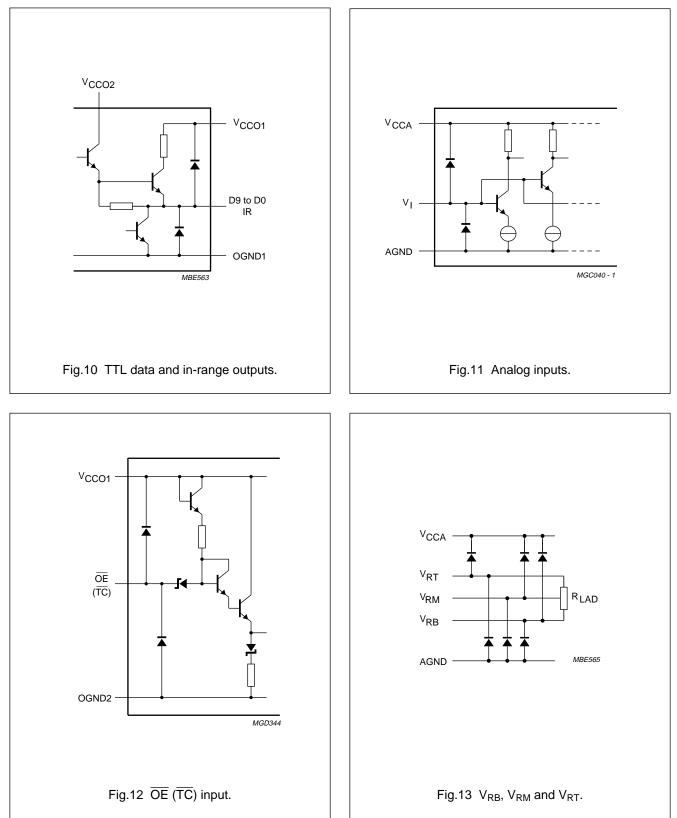

| SYMBOL            | PIN | DESCRIPTION                                          |

|-------------------|-----|------------------------------------------------------|

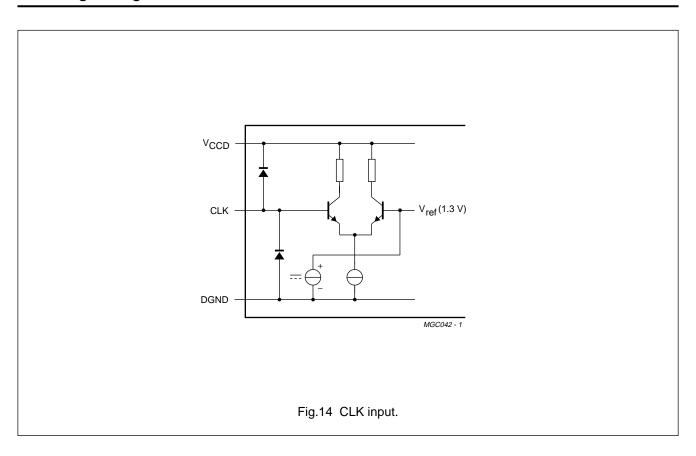

| CLK               | 1   | clock input                                          |

| TC                | 2   | two's complement input (active LOW)                  |

| V <sub>CCA</sub>  | 3   | analog supply voltage (5 V)                          |

| AGND1             | 4   | analog ground 1                                      |

| AGND2             | 5   | analog ground 2                                      |

| V <sub>RB</sub>   | 6   | reference voltage BOTTOM input                       |

| V <sub>RM</sub>   | 7   | reference voltage MIDDLE                             |

| VI                | 8   | analog input voltage                                 |

| V <sub>RT</sub>   | 9   | reference voltage TOP input                          |

| ŌĒ                | 10  | output enable input<br>(TTL level input, active LOW) |

| V <sub>CCD</sub>  | 11  | digital supply voltage (5 V)                         |

| DGND              | 12  | digital ground                                       |

| V <sub>CCO1</sub> | 13  | supply voltage for output stages 1<br>(5 V)          |

| OGND1             | 14  | output ground 1                                      |

| n.c.              | 15  | not connected                                        |

| D0                | 16  | data output; bit 0 (LSB)                             |

| D1                | 17  | data output; bit 1                                   |

| D2                | 18  | data output; bit 2                                   |

| D3                | 19  | data output; bit 3                                   |

| D4                | 20  | data output; bit 4                                   |

| D5                | 21  | data output; bit 5                                   |

| D6                | 22  | data output; bit 6                                   |

| D7                | 23  | data output; bit 7                                   |

| D8                | 24  | data output; bit 8                                   |

| D9                | 25  | data output; bit 9 (MSB)                             |

| IR                | 26  | in range data output                                 |

| OGND2             | 27  | output ground 2                                      |

| V <sub>CCO2</sub> | 28  | supply voltage for output stages 2<br>(5 V)          |

## TDA8762A

#### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                | PARAMETER                                           | CONDITIONS         | MIN. | MAX.             | UNIT |

|-----------------------|-----------------------------------------------------|--------------------|------|------------------|------|

| V <sub>CCA</sub>      | analog supply voltage                               | note 1             | -0.3 | +7.0             | V    |

| V <sub>CCD</sub>      | digital supply voltage                              | note 1             | -0.3 | +7.0             | V    |

| V <sub>cco</sub>      | output stages supply voltage                        | note 1             | -0.3 | +7.0             | V    |

| $\Delta V_{CC}$       | supply voltage difference                           |                    |      |                  |      |

|                       | V <sub>CCA</sub> – V <sub>CCD</sub>                 |                    | -1.0 | +1.0             | V    |

|                       | V <sub>CCA</sub> – V <sub>CCO</sub>                 |                    | -1.0 | +1.0             | V    |

|                       | V <sub>CCD</sub> – V <sub>CCO</sub>                 |                    | -1.0 | +1.0             | V    |

| VI                    | input voltage                                       | referenced to AGND | -0.3 | +7.0             | V    |

| V <sub>clk(p-p)</sub> | AC input voltage for switching (peak-to-peak value) | referenced to DGND | _    | V <sub>CCD</sub> | V    |

| Io                    | output current                                      |                    | -    | 10               | mA   |

| T <sub>stg</sub>      | storage temperature                                 |                    | -55  | +150             | °C   |

| T <sub>amb</sub>      | operating ambient temperature                       |                    | 0    | +70              | °C   |

| Tj                    | junction temperature                                |                    | _    | +150             | °C   |

#### Note

1. The supply voltages V<sub>CCA</sub>, V<sub>CCD</sub> and V<sub>CCO</sub> may have any value between –0.3 and +7.0 V provided that the supply voltage differences  $\Delta V_{CC}$  are respected.

#### HANDLING

Inputs and outputs are protected against electrostatic discharges in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling integrated circuits.

#### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air | 110   | K/W  |

### CHARACTERISTICS

$V_{CCA} = V_3$  to  $V_4$  and  $V_5 = 4.75$  to 5.25 V;  $V_{CCD} = V_{11}$  to  $V_{12} = 4.75$  to 5.25 V;  $V_{CCO} = V_{13}$  and  $V_{28}$  to  $V_{14}$  and  $V_{27} = 4.4$  to 5.25 V; AGND and DGND shorted together;  $T_{amb} = 0$  to +70 °C; typical values measured at  $V_{CCA} = V_{CCD} = V_{CCO} = 5$  V;  $V_{I(p-p)} = 2.0$  V;  $C_L = 15$  pF and  $T_{amb} = 25$  °C; unless otherwise specified.

| SYMBOL           | PARAMETER                                | CONDITIONS                         | MIN.  | TYP. | MAX.             | UNIT |

|------------------|------------------------------------------|------------------------------------|-------|------|------------------|------|

| Supply           |                                          |                                    |       |      | 1                |      |

| V <sub>CCA</sub> | analog supply voltage                    |                                    | 4.75  | 5.0  | 5.25             | V    |

| V <sub>CCD</sub> | digital supply voltage                   |                                    | 4.75  | 5.0  | 5.25             | V    |

| V <sub>CCO</sub> | output stages supply voltage             |                                    | 4.4   | 5.0  | 5.25             | V    |

| $\Delta V_{CC}$  | voltage difference                       |                                    |       |      |                  |      |

|                  | V <sub>CCA</sub> – V <sub>CCD</sub>      |                                    | -0.25 | _    | +0.25            | V    |

|                  | V <sub>CCA</sub> – V <sub>CCO</sub>      |                                    | -0.4  | _    | +0.4             | V    |

|                  | $V_{CCD} - V_{CCO}$                      |                                    | -0.4  | _    | +0.4             | V    |

| I <sub>CCA</sub> | analog supply current                    |                                    | -     | 29   | 36               | mA   |

| I <sub>CCD</sub> | digital supply current                   |                                    | -     | 24   | 30               | mA   |

| I <sub>CCO</sub> | output stages supply current             | C <sub>L</sub> = 15 pF; ramp input | -     | 23   | 30               | mA   |

| Inputs           |                                          |                                    |       |      |                  |      |

| CLOCK INP        | UT CLK (REFERENCED TO DGND);             | note 1                             |       |      |                  |      |

| V <sub>IL</sub>  | LOW level input voltage                  |                                    | 0     | -    | 0.8              | V    |

| V <sub>IH</sub>  | HIGH level input voltage                 |                                    | 2.0   | _    | V <sub>CCD</sub> | V    |

| IIL              | LOW level input current                  | V <sub>clk</sub> = 0.4 V           | -1    | 0    | +1               | μΑ   |

| I <sub>IH</sub>  | HIGH level input current                 | V <sub>clk</sub> = 2.7 V           | -     | -    | 20               | μA   |

| ZI               | input impedance                          | f <sub>clk</sub> = 80 MHz          | -     | 2    | -                | kΩ   |

| CI               | input capacitance                        | f <sub>clk</sub> = 80 MHz          | -     | 2    | -                | pF   |

| INPUTS OE        | AND $\overline{TC}$ (REFERENCED TO DGND) | ; see Table 2                      |       |      |                  |      |

| V <sub>IL</sub>  | LOW level input voltage                  |                                    | 0     | _    | 0.8              | V    |

| VIH              | HIGH level input voltage                 |                                    | 2.0   | _    | V <sub>CCD</sub> | V    |

| IIL              | LOW level input current                  | V <sub>IL</sub> = 0.4 V            | -400  | _    | -                | μΑ   |

| I <sub>IH</sub>  | HIGH level input current                 | V <sub>IH</sub> = 2.7 V            | -     | _    | 20               | μΑ   |

|                  | BINPUT VOLTAGE REFERENCED TO A           | (GND)                              |       |      |                  |      |

| IIL              | LOW level input current                  | V <sub>I</sub> = 1.3 V             | _     | 0    | _                | μA   |

| I <sub>IH</sub>  | HIGH level input current                 | V <sub>1</sub> = 3.8 V             | _     | 70   | -                | μA   |

| ZI               | input impedance                          | f <sub>i</sub> = 4.43 MHz          | _     | 5    | -                | kΩ   |

| CI               | input capacitance                        | f <sub>i</sub> = 4.43 MHz          | -     | 8    | -                | pF   |

| SYMBOL                | PARAMETER                                        | CONDITIONS                                                    | MIN. | TYP.        | MAX.                     | UNIT        |

|-----------------------|--------------------------------------------------|---------------------------------------------------------------|------|-------------|--------------------------|-------------|

| Reference             | e voltages for the resistor ladder;              | see Table 1                                                   | ł    | ł           | 1                        |             |

| V <sub>RB</sub>       | reference voltage BOTTOM                         |                                                               | 1.2  | 1.3         | _                        | V           |

| V <sub>RT</sub>       | reference voltage TOP                            |                                                               | _    | 3.8         | V <sub>CCA</sub> – 0.8 V | V           |

| V <sub>diff</sub>     | differential reference voltage $V_{RT} - V_{RB}$ |                                                               | 1.8  | 2.5         | 3.0                      | V           |

| I <sub>ref</sub>      | reference current                                |                                                               | -    | 28          | -                        | mA          |

| R <sub>LAD</sub>      | resistor ladder                                  |                                                               | _    | 90          | -                        | Ω           |

| TC <sub>RLAD</sub>    | temperature coefficient of the resistor ladder   |                                                               | _    | 1860<br>167 | -                        | ppm<br>mΩ/K |

| V <sub>osB</sub>      | offset voltage BOTTOM                            | note 2                                                        | _    | 220         | _                        | mV          |

| V <sub>osT</sub>      | offset voltage TOP                               | note 2                                                        | _    | 220         | _                        | mV          |

| V <sub>I(p-p)</sub>   | analog input voltage<br>(peak-to-peak value)     | note 3                                                        | 1.5  | 2.06        | 2.5                      | V           |

| Outputs               |                                                  |                                                               | l    | .!          |                          |             |

| DIGITAL OU            | TPUTS D9 TO D0 AND IR (REFERENCE                 | d to OGND)                                                    |      |             |                          |             |

| V <sub>OL</sub>       | LOW level output voltage                         | I <sub>O</sub> = 1 mA                                         | 0    | _           | 0.4                      | V           |

| V <sub>OH</sub>       | HIGH level output voltage                        | I <sub>O</sub> = 0 mA                                         | 2.7  | _           | V <sub>CCO</sub> - 0.5   | V           |

|                       |                                                  | I <sub>O</sub> = -0.4 mA                                      | 2.7  | _           | V <sub>CCO</sub> – 1.3   | V           |

|                       |                                                  | I <sub>O</sub> = -1 mA                                        | 2.4  | _           | V <sub>CCO</sub> - 1.4   | V           |

| I <sub>OZ</sub>       | output current in 3-state mode                   | $0.4 \text{ V} < \text{V}_{\text{O}} < \text{V}_{\text{CCO}}$ | -20  | _           | +20                      | μA          |

| Switching             | characteristics                                  |                                                               |      |             |                          |             |

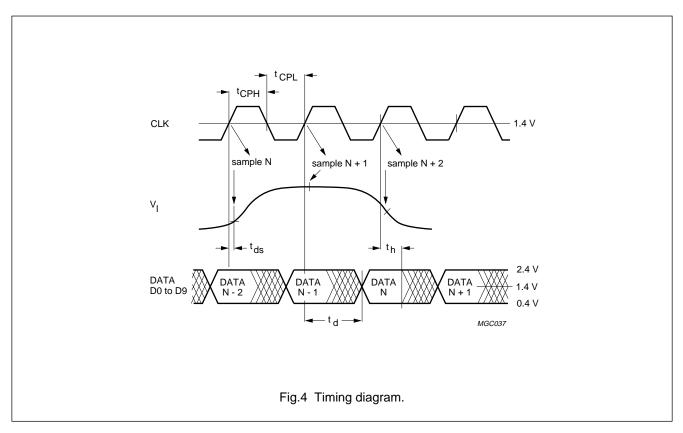

| CLOCK INP             | UT CLK; see Fig.4; note 1                        |                                                               |      |             |                          |             |

| f <sub>clk(max)</sub> | maximum clock frequency                          |                                                               |      |             |                          |             |

|                       | TDA8762A/6                                       |                                                               | 60   | _           | _                        | MHz         |

|                       | TDA8762A/8                                       |                                                               | 80   | _           | _                        | MHz         |

| t <sub>CPH</sub>      | clock pulse width HIGH                           |                                                               | 5    | _           | -                        | ns          |

| t <sub>CPL</sub>      | clock pulse width LOW                            |                                                               | 5    | _           | -                        | ns          |

| Analog sig            | gnal processing                                  |                                                               | ·    |             | •                        |             |

| LINEARITY             |                                                  |                                                               |      |             |                          |             |

| INL                   | integral non-linearity                           | f <sub>clk</sub> = 80 MHz; ramp input                         | -    | ±0.75       | ±1.5                     | LSB         |

| DNL                   | differential non-linearity                       | f <sub>clk</sub> = 80 MHz; ramp input                         | -    | ±0.3        | ±0.7                     | LSB         |

| OFER                  | offset error                                     | middle code; $V_{RB}$ = 1.3 V; $V_{RT}$ = 3.8 V               | -    | ±1          | -                        | LSB         |

| GER                   | gain error (from device to device)               | V <sub>RB</sub> = 1.3 V; V <sub>RT</sub> = 3.8 V;<br>note 4   | -    | ±0.1        | -                        | %           |

|                       |                                                  | •                                                             |      | -           |                          |             |

| SYMBOL            | PARAMETER                                 | CONDITIONS                                                                                         | MIN. | TYP.              | MAX. | UNIT             |

|-------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------|------|-------------------|------|------------------|

| BANDWIDTH         | H (f <sub>clk</sub> = 80 MHz)             | 1                                                                                                  | 1    | 1                 | ł    |                  |

| В                 | analog bandwidth                          | full-scale sine wave; note 5                                                                       | -    | 40                | -    | MHz              |

|                   |                                           | 75% full-scale sine wave;<br>note 5                                                                | -    | 55                | -    | MHz              |

|                   |                                           | small signal at mid-scale;<br>V <sub>I</sub> = $\pm$ 10 LSB at code 512;<br>note 5                 | -    | 700               | -    | MHz              |

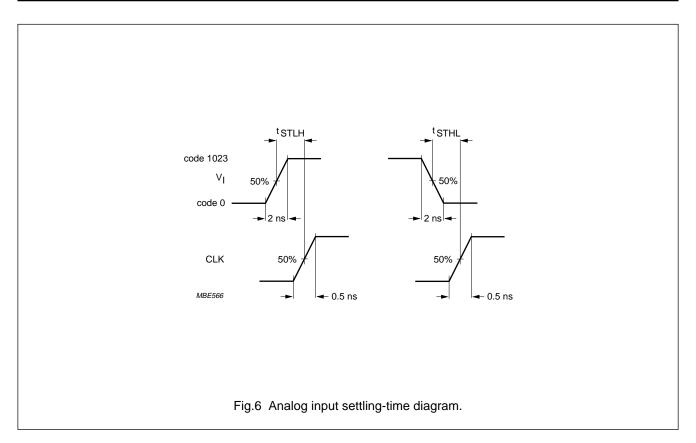

| t <sub>STLH</sub> | analog input settling time<br>LOW-to-HIGH | full-scale square wave;<br>see Fig.6; note 6                                                       | -    | 2.0               | 3    | ns               |

| t <sub>STHL</sub> | analog input settling time<br>HIGH-to-LOW | full-scale square wave;<br>see Fig.6; note 6                                                       | -    | 2.5               | 3.5  | ns               |

| HARMONIC          | s (f <sub>clk</sub> = 80 MHz)             | •                                                                                                  |      | •                 | •    |                  |

| h <sub>1</sub>    | fundamental harmonics (full scale)        | f <sub>i</sub> = 4.43 MHz                                                                          | -    | -                 | 0    | dB               |

| h <sub>all</sub>  | harmonics (full scale);<br>all components | f <sub>i</sub> = 4.43 MHz                                                                          |      |                   |      |                  |

|                   | second harmonics                          |                                                                                                    | -    | -70               | 62   | dB               |

|                   | third harmonics                           |                                                                                                    | -    | -75               | 67   | dB               |

| THD               | total harmonic distortion                 | f <sub>i</sub> = 4.43 MHz                                                                          | _    | -68               | -    | dB               |

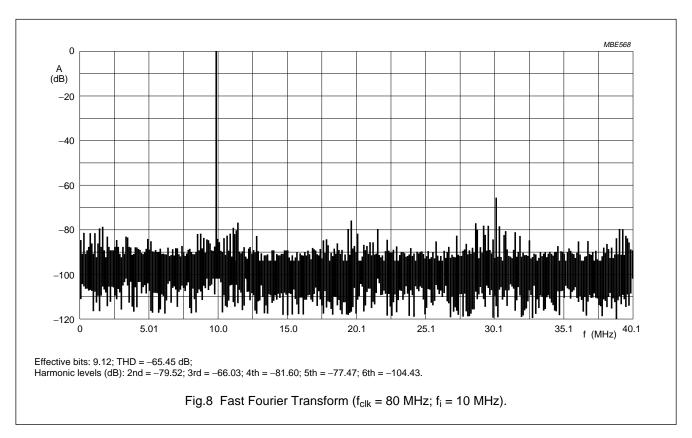

| SIGNAL-TO-        | -NOISE RATIO; see Fig.8; note 7           |                                                                                                    |      |                   |      |                  |

| S/N               | signal-to-noise ratio (full scale)        | without harmonics;<br>$f_{clk} = 80 \text{ MHz};$<br>$f_i = 4.43 \text{ MHz}$                      | 56   | 58                | -    | dB               |

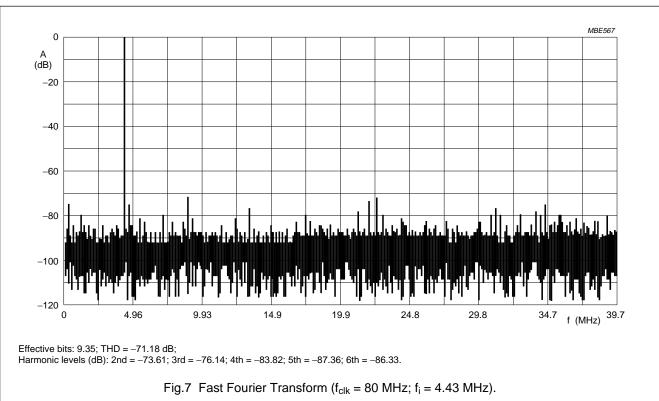

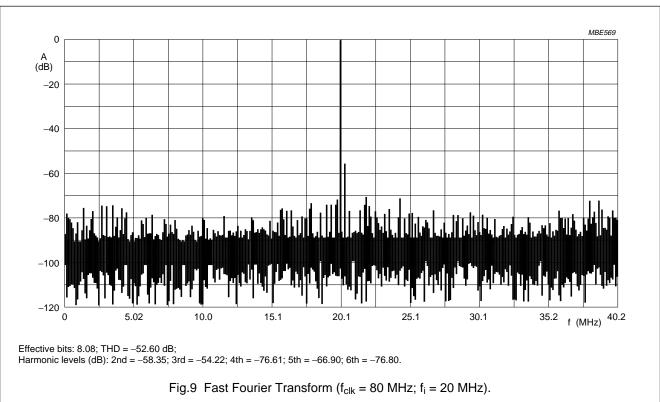

| EFFECTIVE         | BITS; see Figs 7, 8 and 9; note 7         |                                                                                                    |      |                   |      |                  |

| EB                | effective bits                            |                                                                                                    |      |                   |      |                  |

|                   | TDA8762AM/6                               | f <sub>clk</sub> = 60 MHz                                                                          |      |                   |      |                  |

|                   |                                           | f <sub>i</sub> = 4.43 MHz                                                                          | _    | 9.35              | _    | bits             |

|                   |                                           | f <sub>i</sub> = 10 MHz                                                                            | _    | 9.0               | _    | bits             |

|                   |                                           | f <sub>i</sub> = 20 MHz                                                                            | _    | 8.1               | _    | bits             |

|                   | TDA8762AM/8                               | f <sub>clk</sub> = 80 MHz                                                                          |      |                   |      |                  |

|                   |                                           | f <sub>i</sub> = 4.43 MHz                                                                          | -    | 9.3               | _    | bits             |

|                   |                                           | f <sub>i</sub> = 10 MHz                                                                            | -    | 8.9               | _    | bits             |

|                   |                                           | f <sub>i</sub> = 20 MHz                                                                            | -    | 8.0               | _    | bits             |

| TWO-TONE          | ; note 8                                  |                                                                                                    |      |                   |      |                  |

| TTIR              | two-tone intermodulation rejection        | f <sub>clk</sub> = 80 MHz                                                                          | _    | -68               | -    | dB               |

| BIT ERROR         | RATE                                      |                                                                                                    |      |                   | 1    |                  |

| BER               | bit error rate                            | $f_{clk} = 80 \text{ MHz};$<br>$f_i = 4.43 \text{ MHz};$<br>$V_1 = \pm 16 \text{ LSB}$ at code 512 | _    | 10 <sup>-13</sup> | -    | times/<br>sample |

## TDA8762A

| SYMBOL                 | PARAMETER                                             | CONDITIONS                                       | MIN. | TYP. | MAX. | UNIT |

|------------------------|-------------------------------------------------------|--------------------------------------------------|------|------|------|------|

| DIFFERENT              | IAL GAIN; note 9                                      |                                                  | ļ    |      | ļ    | ļ    |

| G <sub>diff</sub>      | differential gain                                     | f <sub>clk</sub> = 80 MHz;<br>PAL modulated ramp | -    | 0.5  | -    | %    |

| DIFFERENT              | TAL PHASE; note 9                                     |                                                  |      |      |      |      |

| φdiff                  | differential phase                                    | f <sub>clk</sub> = 80 MHz;<br>PAL modulated ramp | -    | 0.5  | -    | deg  |

| Timing (f <sub>c</sub> | <b>Ik = 80 MHz; C<sub>L</sub> = 15 pF);</b> see Fig.₄ | 1; note 10                                       |      |      |      |      |

| t <sub>ds</sub>        | sampling delay time                                   |                                                  | -    | -    | 2    | ns   |

| t <sub>h</sub>         | output hold time                                      |                                                  | 5    | -    | -    | ns   |

| t <sub>d</sub>         | output delay time                                     |                                                  | _    | 9    | 13   | ns   |

| CL                     | digital output load capacitance                       |                                                  | -    | 15   | 20   | pF   |

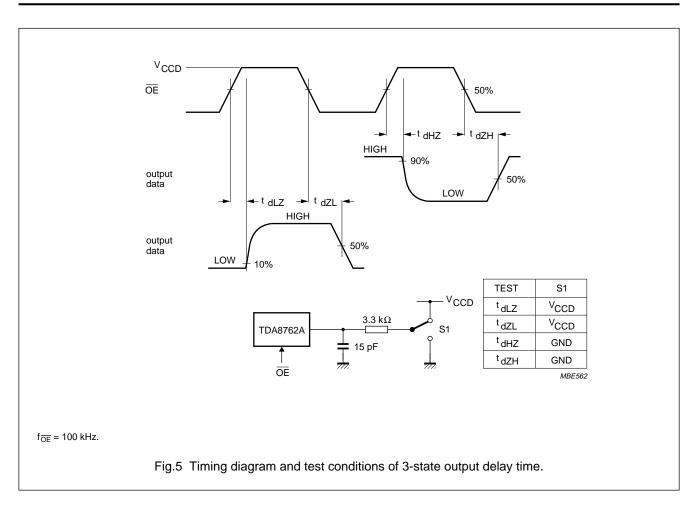

| 3-state ou             | t <b>put delay times;</b> see Fig.5                   |                                                  |      | ł    |      |      |

| t <sub>dZH</sub>       | enable HIGH                                           |                                                  | -    | 45   | 50   | ns   |

| t <sub>dZL</sub>       | enable LOW                                            |                                                  | _    | 25   | 35   | ns   |

| t <sub>dHZ</sub>       | disable HIGH                                          |                                                  | -    | 12   | 15   | ns   |

| t <sub>dLZ</sub>       | disable LOW                                           |                                                  | _    | 12   | 15   | ns   |

#### Notes

- 1. In addition to a good layout of the digital and analog ground, it is recommended that the rise and fall times of the clock must not be less than 0.5 ns.

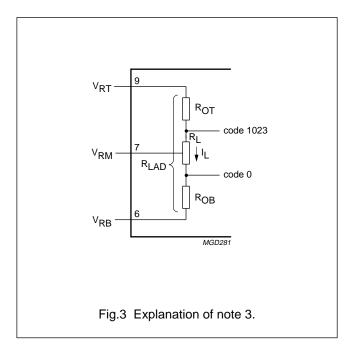

- 2. Analog input voltages producing code 0 up to and including code 1023:

- a) V<sub>osB</sub> (voltage offset BOTTOM) is the difference between the analog input which produces data equal to 00 and the reference voltage BOTTOM (V<sub>RB</sub>) at T<sub>amb</sub> = 25 °C.

- b)  $V_{osT}$  (voltage offset TOP) is the difference between  $V_{RT}$  (reference voltage TOP) and the analog input which produces data outputs equal to code 1023 at  $T_{amb} = 25$  °C.

- In order to ensure the optimum linearity performance of such converter architecture the lower and upper extremities of the converter reference resistor ladder (corresponding to output codes 0 and 1023 respectively) are connected to pins V<sub>RB</sub> and V<sub>RT</sub> via offset resistors R<sub>OB</sub> and R<sub>OT</sub> as shown in Fig.3.

- a) The current flowing into the resistor ladder is  $I_L = \frac{V_{RT} V_{RB}}{R_{OB} + R_L + R_{OT}}$  and the full-scale input range at the converter,

to cover code 0 to code 1023, is

$$V_{I} = R_{L} \times I_{L} = \frac{R_{L}}{R_{OB} + R_{L} + R_{OT}} \times (V_{RT} - V_{RB}) = 0.824 \times (V_{RT} - V_{RB})$$

b) Since R<sub>L</sub>, R<sub>OB</sub> and R<sub>OT</sub> have similar behaviour with respect to process and temperature variation, the ratio

$\frac{R_L}{R_{OB} + R_L + R_{OT}}$  will be kept reasonably constant from part to part. Consequently variation of the output codes

at a given input voltage depends mainly on the difference  $V_{RT} - V_{RB}$  and its variation with temperature and supply voltage. When several ADCs are connected in parallel and fed with the same reference source, the matching between each of them is then optimized.

4. GER =

$$\frac{(V_{1023} - V_0) - 2V}{2V} \times 100$$

1996 Mar 21

- 5. The analog bandwidth is defined as the maximum input sine wave frequency which can be applied to the device. No glitches greater than 2 LSBs, neither any significant attenuation are observed in the reconstructed signal.

- 6. The analog input settling time is the minimum time required for the input signal to be stabilized after a sharp full-scale input (square-wave signal) in order to sample the signal and obtain correct output data.

- Effective bits are obtained via a Fast Fourier Transform (FFT) treatment taking 8K acquisition points per equivalent fundamental period. The calculation takes into account all harmonics and noise up to half of the clock frequency (NYQUIST frequency). Conversion to signal-to-noise ratio: S/N = EB × 6.02 + 1.76 dB.

- 8. Intermodulation measured relative to either tone with analog input frequencies of 4.43 MHz and 4.53 MHz. The two input signals have the same amplitude and the total amplitude of both signals provides full scale to the converter.

- 9. Measurement carried out using video analyser VM700A, where the video analog signal is reconstructed through a digital-to-analog converter.

- 10. Output data acquisition: the output data is available after the maximum delay time of t<sub>d</sub>. In the event of a 80 MHz clock operation, the hardware design must take into account the t<sub>d</sub> and t<sub>h</sub> limits with respect to the input characteristics of the acquisition circuit; an external latch will ease the design if output data lines cannot be short to minimize capacitance.

## 10-bit high-speed low-power analog-to-digital converter

| етер | P V <sub>I(p-p)</sub> IR |   | BINARY OUTPUT BITS |    |    |    |    |    |    | TWO'S COMPLEMENT OUTPUT BITS |    |    |    |    |    |    | ;  |    |    |    |    |    |

|------|--------------------------|---|--------------------|----|----|----|----|----|----|------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|

| STEP |                          |   | D9                 | D8 | D7 | D6 | D5 | D4 | D3 | D2                           | D1 | D0 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| U/F  | <1.52                    | 0 | 0                  | 0  | 0  | 0  | 0  | 0  | 0  | 0                            | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0    | 1.52                     | 1 | 0                  | 0  | 0  | 0  | 0  | 0  | 0  | 0                            | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1    |                          | 1 | 0                  | 0  | 0  | 0  | 0  | 0  | 0  | 0                            | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| -    |                          |   |                    |    |    |    |    |    | -  |                              |    |    |    |    |    |    |    |    |    |    |    |    |

|      |                          |   |                    |    |    |    |    |    | •  |                              |    |    |    |    |    |    |    |    | •  |    |    |    |

| 1022 |                          | 1 | 1                  | 1  | 1  | 1  | 1  | 1  | 1  | 1                            | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| 1023 | 3.58                     | 1 | 1                  | 1  | 1  | 1  | 1  | 1  | 1  | 1                            | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| O/F  | >3.58                    | 0 | 1                  | 1  | 1  | 1  | 1  | 1  | 1  | 1                            | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Table 1 Output coding and input voltage (typical values; referenced to AGND,  $V_{RB} = 1.3 \text{ V}, V_{RT} = 3.8 \text{ V}$ )

### Table 2 Mode selection

| TC | ŌĒ | D9 TO D0                 | IR             |

|----|----|--------------------------|----------------|

| X  | 1  | high impedance           | high impedance |

| 0  | 0  | active; two's complement | active         |

| 1  | 0  | active; binary           | active         |

## TDA8762A

### INTERNAL PIN CONFIGURATIONS

#### **APPLICATION INFORMATION**

The analog and digital supplies should be separated and decoupled.

The external voltage reference generator must be built such that a good supply voltage ripple rejection is achieved with respect to the LSB value. Eventually, the reference ladder voltages can be derived from a well regulated  $V_{CCA}$  supply through a resistor bridge and a decoupled capacitor. (1)  $V_{RB}$ ,  $V_{RM}$  and  $V_{RT}$  are decoupled to AGND.

(2) Pin 15 should be connected to DGND in order to prevent noise influence.

(3) When V<sub>RM</sub> is not used, pin 7 can be left open, avoiding the decoupling capacitor. In any case, this pin must not be grounded.

(4) When analog input signal is AC coupled, an input bias or a clamping level must be applied to  $V_I$  input (pin 8).

Fig.15 Application diagram.

## 10-bit high-speed low-power analog-to-digital converter

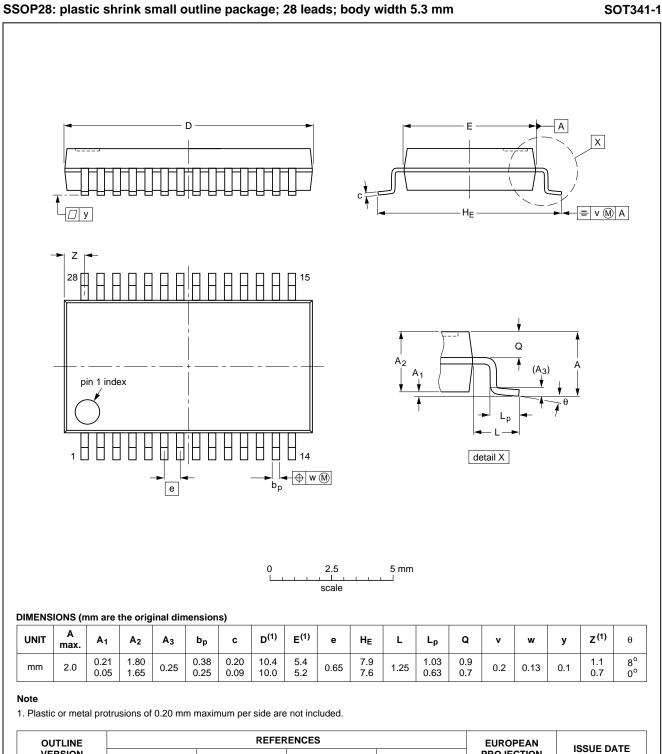

### PACKAGE OUTLINE

| OUTLINE  |     | REFER    | EUROPEAN | ISSUE DATE |            |                                 |

|----------|-----|----------|----------|------------|------------|---------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ     |            | PROJECTION | 1350E DATE                      |

| SOT341-1 |     | MO-150AH |          |            |            | <del>93-09-08</del><br>95-02-04 |

## 10-bit high-speed low-power analog-to-digital converter

### SOLDERING

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"IC Package Databook"* (order code 9398 652 90011).

#### **Reflow soldering**

Reflow soldering techniques are suitable for all SSOP packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45 °C.

#### Wave soldering

Wave soldering is **not** recommended for SSOP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices. If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow and must incorporate solder thieves at the downstream end.

#### Even with these conditions, only consider wave soldering SSOP packages that have a body width of 4.4 mm, that is SSOP16 (SOT369-1) or SSOP20 (SOT266-1).

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### **Repairing soldered joints**

Fix the component by first soldering two diagonallyopposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

#### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                       |

### Application information

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.