#### **Description**

The  $\mu PD4016$  is a 16,384-bit static Random-access Memory device organized as 2,048 words by 8 bits. Using a scaled NMOS technology, its design provides the ease-of-use features associated with nonclocked static memories. The  $\mu PD4016$  has a three-state output and offers a standby mode with an attendant 75% savings in power consumption. It features equal access and cycle times and provides an output enable function that eliminates the need for external bus buffers. The  $\mu PD4016$  is packaged in a 600-mil-wide standard 24-pin dual-in-line package which is plug-compatible with 16K EPROMS .

#### **Features**

| 2.2.0                                               |

|-----------------------------------------------------|

| Scaled NMOS technology                              |

| Completely static memory: no clock, no refresh      |

| Equal access and cycle times                        |

| Single +5V power supply                             |

| Automatic power-down                                |

| All inputs and outputs directly TTL-compatible      |

| Common I/O capability                               |

| OE eliminates need for external bus buffers         |

| Three-state outputs                                 |

| Plug-compatible with 16K 5V EPROMS (600 mil)        |

| Low power dissipation in standby mode               |

| Available in a standard 24-pin dual-in-line package |

| (600-mil width)                                     |

| 4 performance ranges:                               |

|                                                     |

|            | <u> </u>       | R/W           | Power Supply |         |  |  |  |

|------------|----------------|---------------|--------------|---------|--|--|--|

| Device     | Access<br>Time | Cycle<br>Time | Active       | Standby |  |  |  |

| μPD4016C-1 | 250ns          | 250ns         | 60mA         | 15mA    |  |  |  |

| μPD4016C-2 | 200ns          | 200ns         | 60mA         | 15mA    |  |  |  |

| μPD4016C-3 | 150ns          | 150ns         | 60mA         | 15mA    |  |  |  |

| μPD4016C-5 | 120ns          | 120ns         | 60mA         | 15mA    |  |  |  |

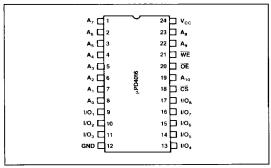

# **Pin Configuration**

### Pin Identification

|                | Pin                                | Description       |

|----------------|------------------------------------|-------------------|

| No.            | Symbol                             | Description       |

| 1-8,<br>22, 23 | A <sub>0</sub> -A <sub>10</sub>    | Address Inputs    |

| 9-11,<br>13-17 | I/O <sub>1</sub> -I/O <sub>8</sub> | Data Input/Output |

| 12             | GND                                | Ground            |

| 18             | <del>CS</del>                      | Chip Select       |

| 20             | ŌE                                 | Output Enable     |

| 21             | WE                                 | Write Enable      |

| 24             | V <sub>CC</sub>                    | + 5V Power Supply |

### **Truth Table**

| CS | ŌĒ | WE | Mode         | I/O              | Power   |

|----|----|----|--------------|------------------|---------|

| Н  | х  | X  | Not Selected | High-Z           | Standby |

| L  | L  | н  | Read         | D <sub>OUT</sub> | Active  |

| L  | н  | L  | Write        | D <sub>IN</sub>  | Active  |

| L  | L  | L  | Write        | D <sub>IN</sub>  | Active  |

#### **Absolute Maximum Ratings\***

| Temperature Under Bias                    | -10°C to +85°C  |

|-------------------------------------------|-----------------|

| Storage Temperature, T <sub>ST</sub>      | -55°C to +125°C |

| Voltage on any Pin with Respect to Ground | -1.5V to +7V    |

| DC Output Current, I <sub>O</sub>         | 20mA            |

| Power Dissipation, Po                     | 1W              |

\*COMMENT: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

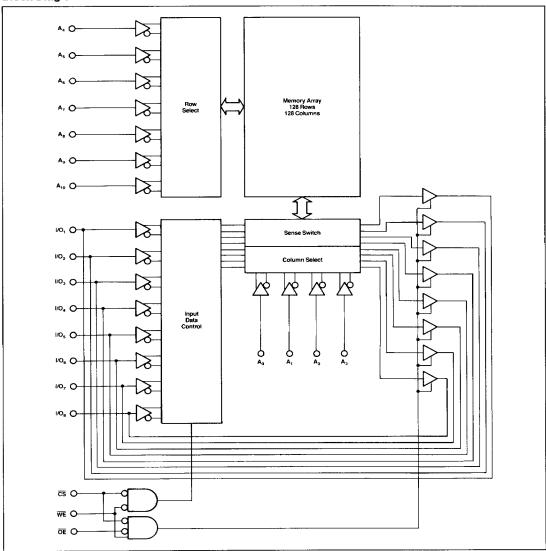

## **Block Diagram**

### Capacitance ①

T<sub>A</sub> = 25°C; f = 1MHz

|                   | -               |     | Limits |     |      | Test                 |

|-------------------|-----------------|-----|--------|-----|------|----------------------|

| Parameter         | Symbol          | Min | Тур    | Max | Unit | Conditions           |

| Input Capacitance | C <sub>IN</sub> |     |        | 5   | рF   | V <sub>IN</sub> = aV |

| I/O Capacitance   | Cia             |     |        | 7   | рF   | $V_{iO} = 0V$        |

Note: 1 This parameter is sampled and not 100% tested.

### **DC** Characteristics

$T_A = 0$ °C to +70°C;  $V_{CC} = 5V \pm 10\%$

|                                 |                 |          | Limits     |     | _          | Test                                                              |

|---------------------------------|-----------------|----------|------------|-----|------------|-------------------------------------------------------------------|

| Parameter                       | Symbol          | Min      | Тур        | Max | Unit       | Conditions ①                                                      |

| Input Leakage Current           | l <sub>U</sub>  |          |            | 10  | μ <b>Α</b> | V <sub>CC</sub> = Max<br>V <sub>IN</sub> = GND to V <sub>CC</sub> |

| Output Leakage<br>Current       | I <sub>LO</sub> |          |            | 10  | μА         | $V_{CC} = Max; \overline{CS} = V_1$<br>$V_{OUT} = GND to V_{CC}$  |

| Operating Current               | Icc             |          |            | 60  | mA         | V <sub>CC</sub> = Max; CS = V <sub>i</sub><br>(outputs open)      |

| Standby Current                 | I <sub>SB</sub> |          |            | 15  | mA         | V <sub>CC</sub> = Min to Max;<br>CS = V <sub>IH</sub>             |

| Input Low Voltage               | VIL             | - 1.5    |            | 0.8 | ٧          |                                                                   |

| Input High Voltage              | VIH             | 2.0      |            | 6.0 | ٧          |                                                                   |

| Output Low Voltage              | VoL             |          |            | 0.4 | v          | I <sub>OL</sub> = 4mA                                             |

| Output High Voltage             | V <sub>OH</sub> | 2.4      |            |     | V          | I <sub>OH</sub> = 1mA                                             |

| Output Short-circuit<br>Current | los             |          | 70         |     | mA         | $V_{OUT} = GND to V_{CC}$                                         |

| Note: 1 Input pulse le          |                 |          | 8V to 2.2  | 2V  |            |                                                                   |

| Input timing re                 | eference level  | ls: 1.   | 5V         |     |            |                                                                   |

| Output timing                   | reference lev   | refs: 1. | 5 <b>V</b> |     |            |                                                                   |

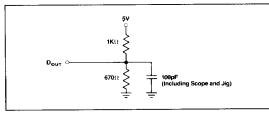

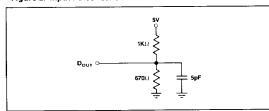

Figure 1. Loading Conditions Test Circuit

Figure 2. Input Pulse Test Circuit

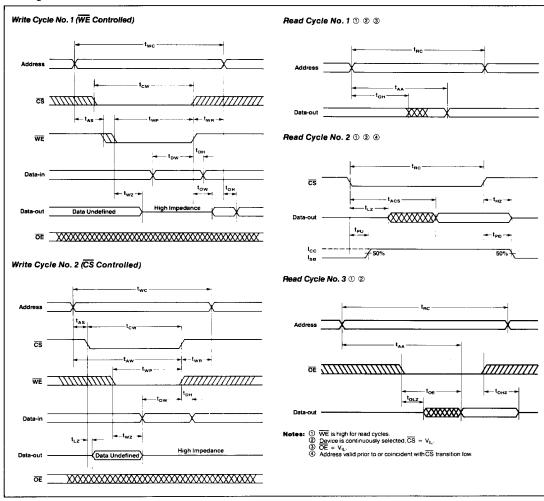

## **AC Characteristics**

$T_A = 0$ °C to +70°C;  $V_{CC} = 5V \pm 10$ % **Read Cycle**

|                                               |                  |        |     |        | Limi | ts ①   |     |        |     |      |            |

|-----------------------------------------------|------------------|--------|-----|--------|------|--------|-----|--------|-----|------|------------|

|                                               |                  | 4016-5 |     | 4016-3 |      | 4016-2 |     | 4016-1 |     | •    |            |

| Parameter                                     | Symbol           | Min    | Max | Min    | Max  | Min    | Max | Min    | Max | Unit | Notes      |

| Read Cycle<br>Time                            | 1 <sub>RC</sub>  | 120    |     | 150    |      | 200    |     | 250    |     | ns   | 2          |

| Address<br>Access Time                        | t <sub>AA</sub>  |        | 120 |        | 150  |        | 200 |        | 250 | ns   |            |

| Chip Select<br>Access Time                    | tacs             |        | 120 |        | 150  |        | 200 |        | 250 | ns   | 3          |

| Output Hold<br>from Address<br>Change         | t <sub>OH</sub>  | 10     |     | 10     |      | 10     |     | 10     |     | ns   |            |

| Chip Selection<br>to Output<br>in Low-Z       | t <sub>LZ</sub>  | 10     |     | 10     |      | 10     |     | 10     |     | ns   | 4 9        |

| Chip<br>Deselection<br>to Output<br>in High-Z | t <sub>HZ</sub>  |        | 45  |        | 50   |        | 60  |        | 80  | ns   | 4 5        |

| Output Enable<br>to Output<br>Valid           | t <sub>OE</sub>  |        | 50  |        | 70   |        | 90  |        | 110 | ns   |            |

| Output Enable<br>to Output<br>in Low-Z        | t <sub>OLZ</sub> | 10     |     | 10     |      | 10     |     | 10     |     | ns   | <b>4 (</b> |

| Output Disable<br>to Output<br>in High-Z      | t <sub>OHZ</sub> |        | 45  |        | 50   |        | 60  |        | 80  | ns   | 4 5        |

| Chip Selection<br>to Power-up<br>Time         | t <sub>PU</sub>  | 0      |     | 0      |      | 0      |     | 0      |     | ns   | (5)        |

| Chip<br>Deselection<br>to Pawer-down<br>Time  | t <sub>PD</sub>  |        | 60  |        | 70   |        | 90  |        | 110 | ns   | (§)        |

### **Write Cycle**

|                                         |                 |     | Limits ① |     |        |     |     |        |     |      |            |

|-----------------------------------------|-----------------|-----|----------|-----|--------|-----|-----|--------|-----|------|------------|

|                                         |                 | 401 | 6-5      | 40  | 4016-3 |     | 6-2 | 4016-1 |     | -    |            |

| Parameter                               | Symbol          | Min | Max      | Min | Max    | Min | Max | Min    | Max | Unit | Notes      |

| Write Cycle<br>Time                     | twc             | 120 |          | 150 |        | 200 |     | 250    |     | ns   |            |

| Chip Selection<br>to End of<br>Write    | t <sub>cw</sub> | 90  |          | 120 |        | 160 |     | 200    |     | ns   |            |

| Address Valid<br>to End of<br>Write     | taw             | 80  |          | 90  |        | 120 |     | 150    |     | ns   |            |

| Address Set-up<br>Time                  | tas             | 0   |          | 0   |        | 0   |     | 0      |     | ns   |            |

| Write Pulse<br>Width                    | twp             | 70  |          | 80  |        | 100 |     | 130    |     | ns   | 6          |

| Write Recovery<br>Time                  | t <sub>WR</sub> | 10  |          | 10  |        | 10  |     | 10     |     | ns   |            |

| Data Valid to<br>End of Write           | t <sub>DW</sub> | 45  |          | 50  |        | 60  |     | 80     |     | nş   |            |

| Data Hold<br>Time                       | t <sub>DH</sub> | 0   |          | 0   |        | 0   |     | 0      |     | ns   |            |

| Write Enabled<br>to Output<br>in High-Z | twz             |     | 45       |     | 50     |     | 60  |        | 80  | ns   | (§) (T)    |

| Output Active<br>from End<br>of Write   | tow             | 10  |          | 10  |        | 10  |     | 10     |     | ns   | <b>⑤</b> ⑦ |

- Notes: See Part No. Package Width table below

Alf read cycle timings are referenced from the last valid address to the first transition address.

Address valid prior to or coincident with CS transition low.

Transition is measured 200mV from sleady-state voltage with specified load of Figure 1.

This parameter is sampled and not 100% tested.

If CS and DE are both low before write enabled, type—tyz—type.

Transition is measured + 200mV from sleady-state voltage with specified load of Figure 2.

7-19

## **Timing Waveforms**