# TH6P04T6V5CL TH6P04T25CL

## TRANSIL ARRAY FOR DATA LINE PROTECTION

#### DESCRIPTION

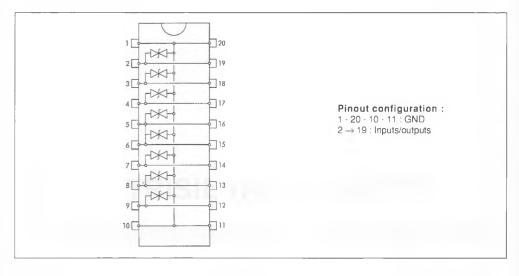

Developed specially for data line protection at the PC Board Level, the component offers 8 protective Bidirectionnal devices with common bus connections per package.

In addition to the parallel protection given by the Transils ®, the pin-die connection wires provide a serie protection in case of short circuit on the line. Therefore this device is a feature of 8 serie/parallel protection elements.

The dual in line design allows compatible packaging for microprocessors, memories and controllers.

#### **ABSOLUTE RATINGS** (limiting values) $(0^{\circ}C \le T_{amb} \le 70^{\circ}C)$

| Symbol                             | Parameter                                      | Value      | Unit               |                  |

|------------------------------------|------------------------------------------------|------------|--------------------|------------------|

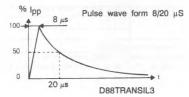

| l <sub>pp</sub>                    | Peak Pulse Power for 8.20 µs Exponential Pulse | See note 1 | 40                 | A                |

| l <sup>2</sup> t                   | Wire I <sup>2</sup> t Value                    | See note 1 | 0.6                | A <sup>2</sup> s |

| ESD                                | Electrostatic Overstress                       | See note 2 | 25                 | kV               |

| T <sub>stg</sub><br>T <sub>j</sub> | Storage and Junction Temperature Range         |            | - 55 to 150<br>125 | °C<br>°          |

Notes: 1. For surges upper than the maximum value specified, the input/output will present first a short circuit to the common bus line and after an open circuit caused by the wire

2. According to MIL STD 883C method 3015-2.

## **ELECTRICAL CHARACTERISTICS**

$0 \ ^{\circ}C \leq T_{amb} = T_{j} \leq 70 \ ^{\circ}C$

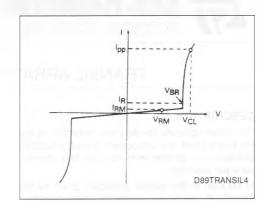

| Symbol          | Parameter                         |  |

|-----------------|-----------------------------------|--|

| VRM             | Stand-off Voltage                 |  |

| V <sub>BR</sub> | Breakdown Voltage                 |  |

| V <sub>CL</sub> | Clamping Voltage                  |  |

| IRM             | Leakage Current @ V <sub>RM</sub> |  |

| lpp             | Surge Current                     |  |

| С               | Input Capacitance                 |  |

| Symbol            | Test Conditions                                                                                                                    | Types        | Min.  | Тур. | Max. | Unit |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------|------|------|

| VBR               | $I_{R} = \pm 1 \text{ mA}$                                                                                                         | TH6P04T6V5CL | ± 6.5 |      |      | V    |

|                   |                                                                                                                                    | TH6P04T25CL  | ± 25  |      |      |      |

| IRM               | V <sub>RM</sub> = ± 6 V                                                                                                            | TH6P04T6V5CL |       |      | ± 50 | μA   |

|                   | $V_{RM} = \pm 24 V$                                                                                                                | TH6P04T25CL  |       |      | ± 10 |      |

| C1                | Each Input Pin to Ground at 0 V Bias                                                                                               | TH6P04T6V5CL |       |      | 700  | pF   |

|                   |                                                                                                                                    | TH6P04T25CL  |       |      | 500  |      |

| C2                | Each Input Pin to Ground at 5 V Bias                                                                                               | TH6P04T6V5CL |       |      | 500  | рF   |

|                   |                                                                                                                                    | TH6P04T25CL  |       |      | 300  |      |

| V <sub>CL</sub> 1 | $I_{pp} = 40 \text{ A}$<br>8-20 $\mu$ s to all Inputs Sequentially (see note 1)                                                    | TH6P04T6V5CL |       |      | ± 12 | V    |

|                   |                                                                                                                                    | TH6P04T25CL  |       |      | ± 38 |      |

| V <sub>CL</sub> 2 | $8\text{-}20\ \mu\text{s}$ Simultaneously 80 A peak pulse current to all inputs with a 10 $\Omega$ resistor in serie. (see note 1) | TH6P04T6V5CL |       |      | ± 12 | V    |

|                   |                                                                                                                                    | TH6P04T25CL  |       |      | ± 35 |      |

| V <sub>CL</sub> 3 | 25 kV ESD Overstress (see notes 1-2)                                                                                               | TH6P04T6V5CL |       |      | ± 12 | V    |

|                   |                                                                                                                                    | TH6P04T25CL  |       |      | ± 35 |      |

Notes : 1. V<sub>CL</sub> mesured on outputs.

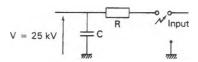

2. According to MIL STD 883C method 3015-2. C = 150 pF R = 150  $\Omega$  F = 10 Hz Exposure = 5 secs.

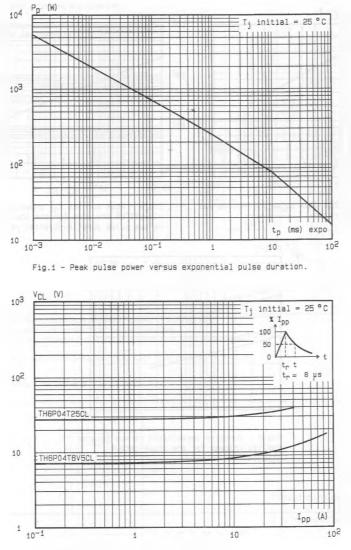

Fig.2 - Clamping voltage versus peak pulse current exponential waveform t =  $20 \ \mu s$ .

Note : The curves of the figure 2 are specified for a junction temperature of 25 °C before surge. The given results may be extrapolated for other junction temperatures by using the following formula :  $\Delta V$  (BR) =  $\alpha T (V (BR)) X [T_j - 25] X V (BR)$  For intermediate voltages, extrapolate the given results. D89TH8P04TP3

## TH6P04T6V5CL/TH6P04T25CL

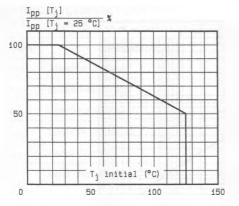

Fig.3 - Allowable peak pulse current versus junction temperature.

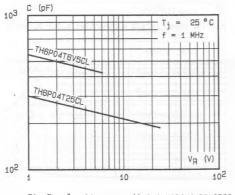

Fig.5 - Junction capacitance versus reverse applied voltage for one input/output (typical values).

D89TH6P04TP4

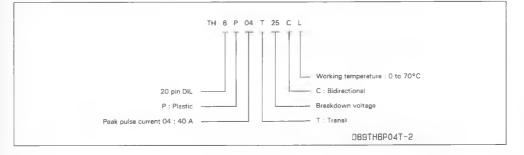

#### ORDER CODE

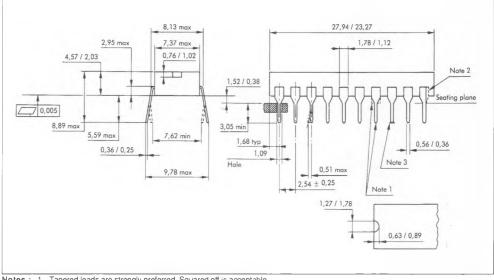

## PACKAGE MECHANICAL DATA

### **DIP-20 Plastic**

Notes: 1. Tapered leads are strongly preferred. Squared off is acceptable.

- 2. Half shoulders are acceptable on four end leads only.

- 3. On blunt tips, allowable burr or spur is .003 in max on either sude of lead.

Packaging : Products supplied in antistatic tubes. Each tubes contains 18 products.

## FUNCTIONNAL DIAGRAM