# **CPH6904**

# http://onsemi.com

# N-Channel JFET 25V, 20 to 40mA, 40mS, Dual CPH6

#### **Features**

- · Composite type with 2 J-FET contained in a CPH6 package currently in use, improving the mounting efficiency greatly

- · The CPH6904 is formed with two chips, being equivalent to the CPH3910, placed in one package

## **Specifications**

#### Absolute Maximum Ratings at Ta=25°C

| Parameter                   | Symbol           | Conditions | Ratings     | Unit |

|-----------------------------|------------------|------------|-------------|------|

| Drain-to-Source Voltage     | VDSX             |            | 25          | V    |

| Gate-to-Source Voltage      | V <sub>GDS</sub> |            | -25         | V    |

| Gate Current                | IG               |            | 10          | mA   |

| Drain Current               | ID               |            | 50          | mA   |

| Allowable Power Dissipation | PD               | 1unit      | 400         | mW   |

| Total Power Dissipation     | PT               |            | 700         | mW   |

| Channel Temperature         | Tch              |            | 150         | °C   |

| Storage Temperature         | Tstg             |            | -55 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

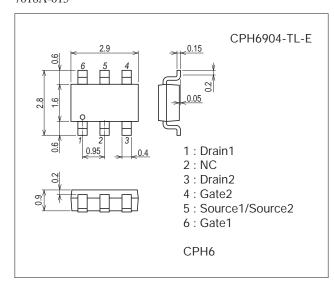

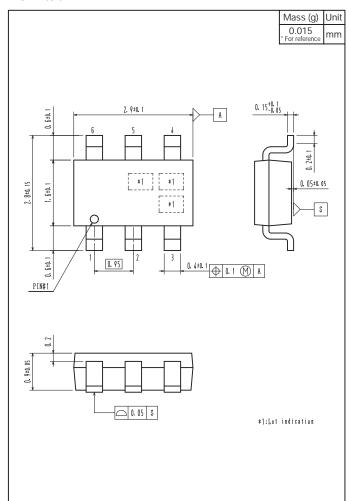

#### **Package Dimensions**

unit : mm (typ) 7018A-015

#### **Product & Package Information**

• Package : CPH6

• JEITA, JEDEC : SC-74, SOT-26, SOT-457

• Minimum Packing Quantity : 3,000 pcs./reel

#### Packing Type: TL

#### Marking

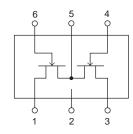

#### **Electrical Connection**

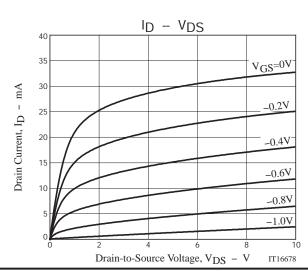

### Electrical Characteristics at Ta=25°C

| Parameter                       | Symbol                | Conditions                                         | Ratings |      |      | Unit |  |

|---------------------------------|-----------------------|----------------------------------------------------|---------|------|------|------|--|

| Parameter                       | Symbol Conditions     |                                                    | min     | typ  | max  | UIII |  |

| Gate-to-Drain Breakdown Voltage | V(BR)GDS              | IG=-10μA, VDS=0V                                   | -25     |      |      | V    |  |

| Gate-to-Source Leakage Current  | IGSS                  | V <sub>GS</sub> =-10V, V <sub>DS</sub> =0V         |         |      | -1.0 | nA   |  |

| Cutoff Voltage                  | V <sub>GS</sub> (off) | V <sub>DS</sub> =5V, I <sub>D</sub> =100μA         | -0.6    | -1.2 | -1.8 | V    |  |

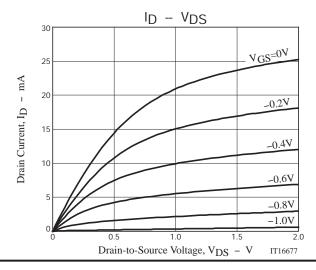

| Drain Current                   | IDSS                  | V <sub>DS</sub> =5V, V <sub>GS</sub> =0V           | 20.0    |      | 40.0 | mA   |  |

| Forward Transfer Admittance     | yfs                   | V <sub>DS</sub> =5V, V <sub>GS</sub> =0V, f=1kHz   | 30      | 40   |      | mS   |  |

| Input Capacitance               | Ciss                  | VDS=5V, VGS=0V, f=1MHz                             |         | 6.0  |      | pF   |  |

| Reverse Transfer Capacitance    | Crss                  | VDS=5V, VGS=0V, I=1IVIHZ                           |         | 2.3  |      | pF   |  |

| Noise Figure                    | NF                    | V <sub>DS</sub> =5V, V <sub>GS</sub> =0V, f=100MHz |         | 2.1  | 2.8  | dB   |  |

The specifications shown above are for each individual J-FET.

# **Ordering Information**

| Device Package |      | Shipping       | memo    |  |

|----------------|------|----------------|---------|--|

| CPH6904-TL-E   | CPH6 | 3,000pcs./reel | Pb Free |  |

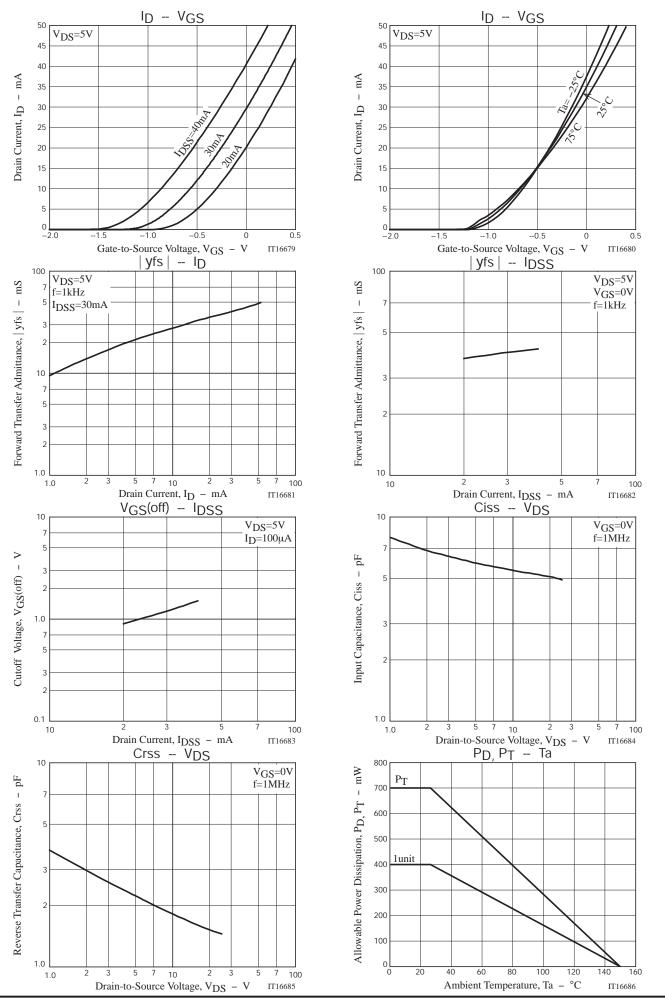

## **Embossed Taping Specification**

#### CPH6904-TL-E

### 1. Packing Format

| Package Name | Carrier Tape | Maximum Number of<br>devices contained (pcs) |           |           | Packing format           |                          |  |

|--------------|--------------|----------------------------------------------|-----------|-----------|--------------------------|--------------------------|--|

|              | Type         | Reel                                         | Inuer pox | Outer box | Inner BOX (C-1)          | Outer BOX (A-7)          |  |

| <br>СРН6     | СРН6         | 3, 000                                       | 15, 000   | 90,000    | 5 reels contained        | 6 inner boxes contained  |  |

|              |              |                                              |           |           | Dimensions:mm (external) | Dimensions:mm (external) |  |

|              |              |                                              |           |           | 183×72×185               | 440×195×210              |  |

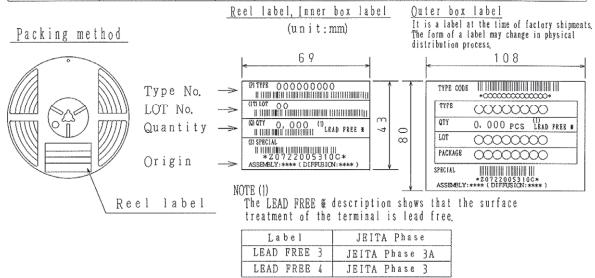

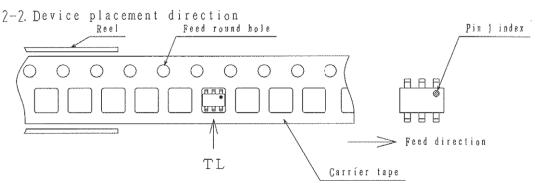

## 2. Taping configuration

#### 2-1. Carrier tape size (unit:mm)

Those with pin 1 index on the feed hole side · · · · · TL

# **Outline Drawing**

## CPH6904-TL-E

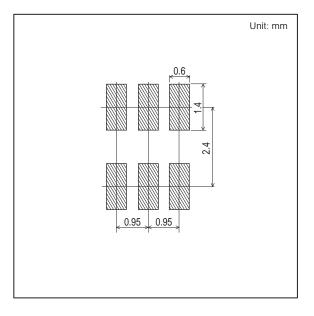

# Land Pattern Example

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa